- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Use Master Reload signal as the source for counter initialization

Use Master Reload signal as the source for counter initialization

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all,

I'm using MPC5744P and trying to use Master Reload signal from submodule 0 as the source for submodule 1 counter initialization.

In submodule 0, I set up reloading point as full-cycle reload and reload every 1 opportunity. As stated in RM "the period of the counter will be locked to the register reload frequency of submodule0". Therefore, I expected the submodule 1 counter to reset when it reaches the modulo value (VAL1) of submodule 0.

The problem here is the submodule 1 counter does not reset at the time master reload signal asserts and it count all the way up to 0xFFFF (maximum register value) then reset.

I'd like to ask if I'm misunderstanding anything or there should be some more configuration to make it work.

Thank you for reading!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Thomas,

yes it behaves as you described. In order to use Master reload to reinit counter the LDOK must be set again each time the reload happen.

Use rather Master sync signal to reinit other submodule's counter.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

did you select source of init signal for the counter using CTRL2[INIT_SEL] bits on submodule1.

Try FlexPWM_x.SUB[1].CTRL2.B.INIT_SEL = 0x1;

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Petr,

Thanks for your reply.

I did set INT_SEL bit to 1.

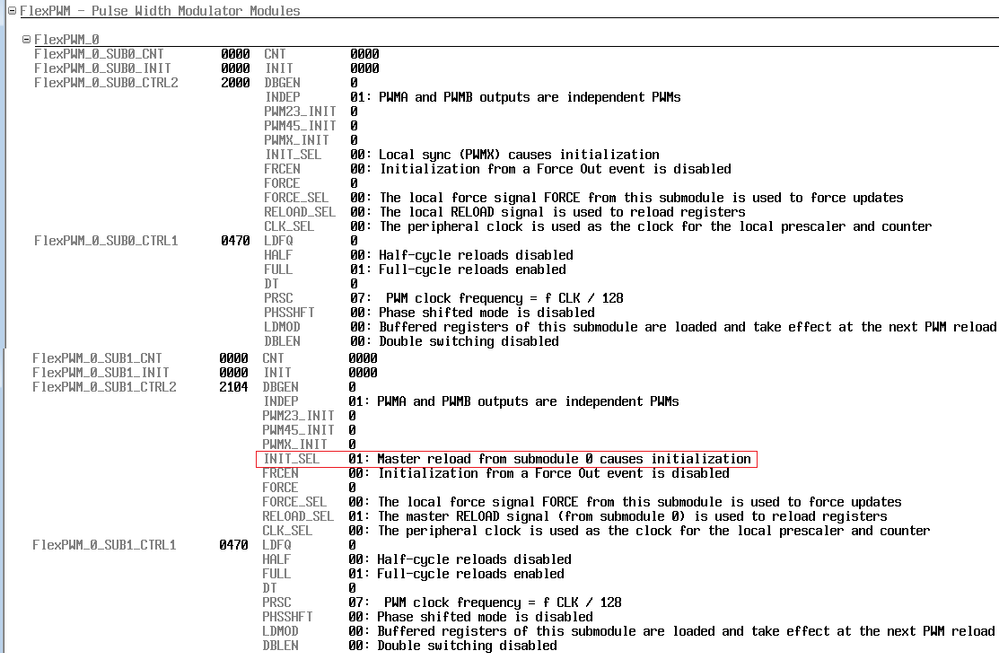

I have attached my CTRL1 and CTRL2 registers set for both submodule 0 and 1.

The result is while submodule 0 outputs expected pwm signal, submodule 1 counter always counts to overflow (0xFFFF)

BRs,

Thomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Thomas,

yes it behaves as you described. In order to use Master reload to reinit counter the LDOK must be set again each time the reload happen.

Use rather Master sync signal to reinit other submodule's counter.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Petr,

I have tested and it works exactly like what you said.

Thank you very much.

BR,

Thomas