- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- QEI Digital filter related

QEI Digital filter related

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

QIZ 1 : FILTA : Digital filter sampling delay , what kind of unit for FILTA?

QIZ2 : how to set FILTA? I need a example of application.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

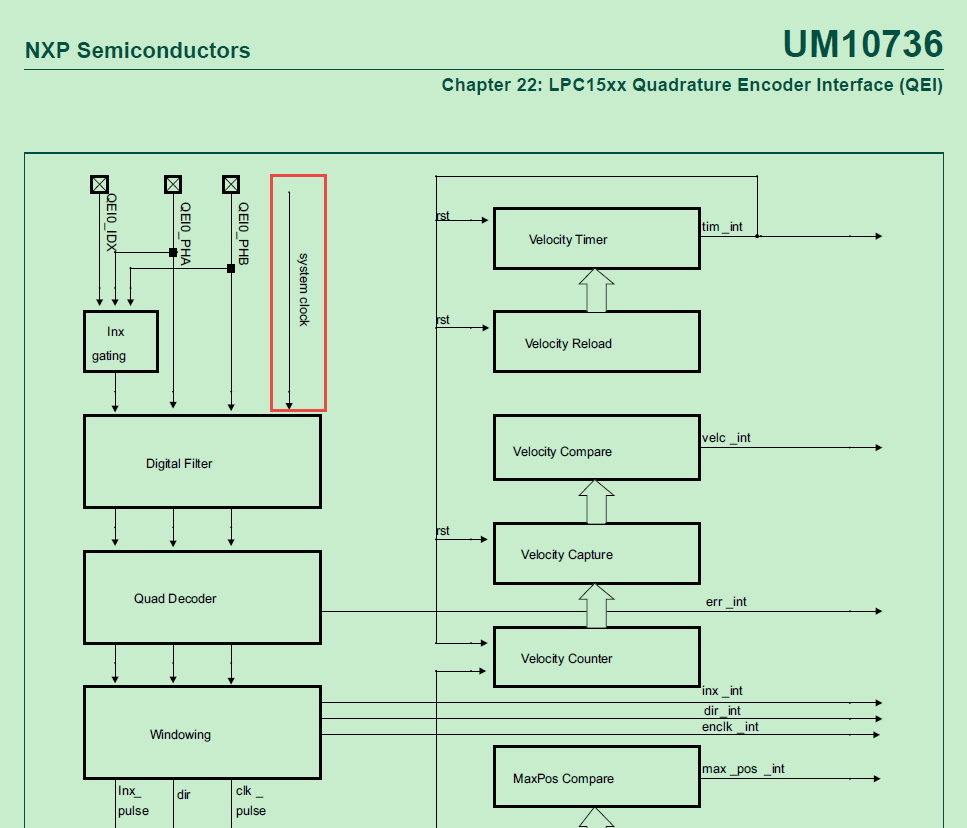

All three encoder inputs (PhA, PhB, and index) require digital filtering.

The number of sample clocks is user programmable from 1 to 4,294,967,295 (0xFFFF FFFF).

The QEI Digital filter on phase A input register [FILTA] bits using to set the filter delay for phA input signal.

From below picture, the digital filter clock source is system clock.

For example:

If customer set the [FILTA] bits value to 0x10000 with system clock 72MHz, the filter delay will be 910us.

If customer set the [FILTA] bits value to 0x10000 with system clock 12MHz, the filter delay will be 5.5ms.

If customer want to filter the input glitch (200ns width), customer can set the [FILTA] bits value to 0x10 with system clock 72MHz.

Wish it helps.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

All three encoder inputs (PhA, PhB, and index) require digital filtering.

The number of sample clocks is user programmable from 1 to 4,294,967,295 (0xFFFF FFFF).

The QEI Digital filter on phase A input register [FILTA] bits using to set the filter delay for phA input signal.

From below picture, the digital filter clock source is system clock.

For example:

If customer set the [FILTA] bits value to 0x10000 with system clock 72MHz, the filter delay will be 910us.

If customer set the [FILTA] bits value to 0x10000 with system clock 12MHz, the filter delay will be 5.5ms.

If customer want to filter the input glitch (200ns width), customer can set the [FILTA] bits value to 0x10 with system clock 72MHz.

Wish it helps.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------