- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K Crystal Transconductance (g_m_xosc) specification

S32K Crystal Transconductance (g_m_xosc) specification

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K Crystal Transconductance (g_m_xosc) specification

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear All,

(Note this question has been edited and simplified from the original post)

I am looking to clarify some of the crystal oscillator specifications for the S32K.

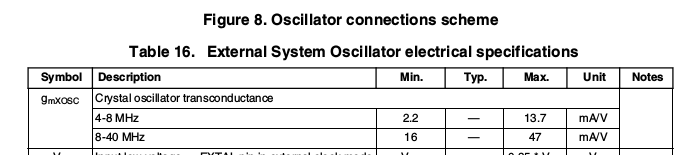

In Table 16 of the S32K datasheet, several values for g_m_xosc are specified:

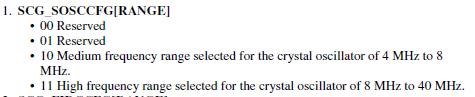

I can see that the 4-8MHz vs the 8-40MHz can be selected through SCG_SOSCCFG (p572 S32K RM), but the datasheet does not seem to provide guidance as to whether the transconductance min/max values of 16mA/V and 47mA/V refer to "low-gain" or "high-gain" operation.

Are there differences in transconductance between these two modes?

Kind regards,

Damien.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Damien,

Those two different transconductances are corresponding to SOSCCFG[RANGE].

The g_m_XOSC would be changed by the SOSCCFG[HGO] setting, but it would still be within the specified min/max range.

With the setting SOSCCFG[HGO]=1 is add an external feedback resistor and SOSCCFG[HGO]=0 means without external feedback resistor.

I hope it helps you.

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

So, if we can guarantee that out gain margin is 5x when using low-gain mode, then no feedback resistor is necessary?

My concern is that if there are no guarantees on the minimum transconductance when using the high-gain mode (separate to the low-gain mode), it makes it very difficult to establish what crystals can be safely used if the 5x gain is not established at the minimum transconductance of 16mA/V (for 8-40Mhz crystals).

It would be most helpful if the datasheet explicitly listed the min/max transconductance for both high and mid-speed crystals in both low-gain and high-gain modes.

Kind regards,

Damien.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Damien,

When low-gain is selected, internal feedback resistor will be selected and external feedback resistor should not be attached.

Could you tell me which parameter is making difficult to achieve the minimum gmXOSC?

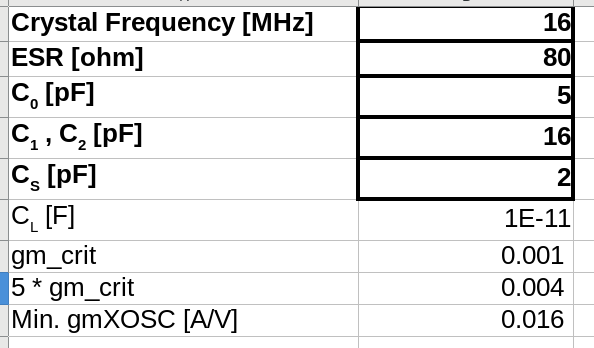

Could you please fill the required parameters in the attached excel sheet? It can help you to calculate the gm_crit.

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

We were targeting the following crystal:

ABM10AIG-16.000MHZ-4Z-T3 Abracon LLC | Crystals, Oscillators, Resonators | DigiKey

The good news is your spreadsheet is similar to what I have previously calculated and it shows sufficient gain margin to use the low-gain mode.

However, there are still a few open questions:

- What role, if any, does the pad resistance of 40R (See Figure 8) have on the gain margin?

- If high-gain mode is selected, what is the minimum transconductance?

If a minimum transconductance figure cannot be guaranteed in high-gain mode (other than the figure in low-gain mode), why have it at all?