- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MQX Software Solutions

- :

- MQX Software Solutions

- :

- MQX 4.2 K24 clock settings

MQX 4.2 K24 clock settings

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've noticed my clock is running slower than it should be. Inside of bsp_cm.c you have the following defines

/* Clock configuration 0 */

#define CPU_MCG_MODE_CONFIG_0 (CPU_MCG_MODE_PEE | CPU_CLOCK_EXTERNAL_CRYSTAL_MASK | CPU_CLOCK_FAST_MASK) /* Clock generator mode */

#define CPU_CLOCK_VLP_CONFIG_0 0U /* RUN power mode */

#define CPU_MCG_C1_CONFIG_0 0x20U /* MCG_C1 */

#define CPU_MCG_C2_CONFIG_0 0x25U /* MCG_C2 */

#define CPU_MCG_C4_CONFIG_0 0x00U /* MCG_C4 */

#define CPU_MCG_C5_CONFIG_0 0x03U /* MCG_C5 */

#define CPU_MCG_C6_CONFIG_0 0x40U /* MCG_C6 */

#define CPU_MCG_SC_CONFIG_0 0x02U /* MCG_SC */

#define CPU_OSC_CR_CONFIG_0 0x80U /* OSC_CR */

#define CPU_SIM_SOPT1_CONFIG_0 0x00080000UL /* SIM_SOPT1 */

#define CPU_SIM_SOPT2_CONFIG_0 0x00010000UL /* SIM_SOPT2 */

#define CPU_SIM_CLKDIV1_CONFIG_0 0x01130000UL /* SIM_CLKDIV1 */

/* Clock configuration 1 */

#define CPU_MCG_MODE_CONFIG_1 (CPU_MCG_MODE_PEE | CPU_CLOCK_EXTERNAL_CRYSTAL_MASK | CPU_CLOCK_FAST_MASK) /* Clock generator mode */

#define CPU_CLOCK_VLP_CONFIG_1 0U /* RUN power mode */

I've hand cranked these values for a 120MHz clock with a 16MHz crystal and they don't match the values above. Anyone know what these values should be given my scenario?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ryan

There are two possibilities for configuring the K24 for 120MHz PLL operation from a 16 MHz crystal (120MHz core, 60MHz bus, 24MHz flash, 40MHz FlexBus clock [some bits are optional or flags and don't directly influencing the frequency]):

1:

MCG_C2 = 0xa4;

MCG_C5 = 0x23;

MCG_C6 = 0x46;

SIM_CLKDIV1 = 0x01240000

MCG_C1 = 0x28

2:

MCG_C2 = 0xa0;

MCG_C5 = 0x25;

MCG_C6 = 0x55;

SIM_CLKDIV1 = 0x01240000

MCG_C1 = 0x28

The values that you have for SIM_CLKDIV1 look suspect since they would give 30MHz Flash and 60MHz FlexClock, which are both out or spec for the K24. This makes me believe that the setup must be for a lower core clock speed (such as 96Mhz) where they would be just in spec.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Ryan,

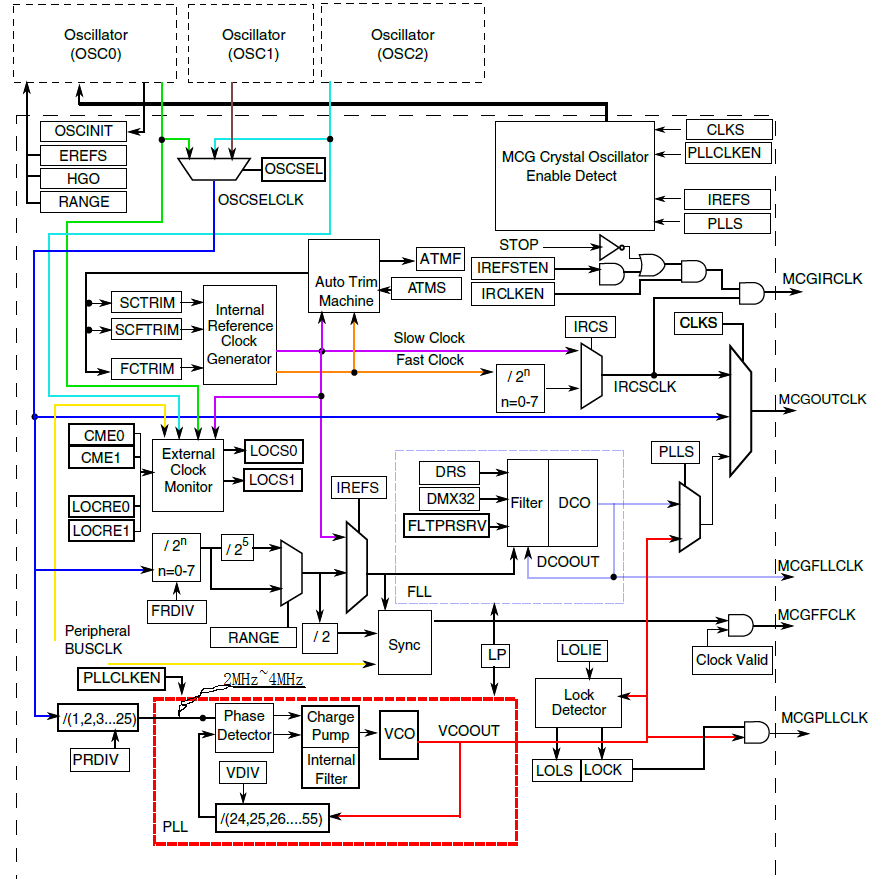

I copy the MCG diagram here. The external clock is 16MHz, the PLL input clock frequency range is limited from 2MHz to 4mHz, the VCOOUT clock frequency is from 48MHz to 120MHz, the VDIV is from 24 to 55.

The VCOOUT clock frequency=(external clock frequency)*VDIV/PRDIV.

If PRDIV=4, the PLL input clock frequency is 16MHz/4=4MHz. If the VDIV=30, the VCOOUT clock frequency is 16*30/4=120MHz.

If the PRDIV=8, the PLL input clock frequency is 16MHz/8=2MHz. If the VDIV=55, the VCOOUT clock frequency is 16*55/8=110MHz. Of course, this is not an option if you want to get 120MHz.

if PRDIV=6, VDIV=45, the VCOOUT frequency is 16MHz*45/6=120MHz, the PLL input frequency is 16MHz/6=2.66MHz, it is okay.

Mark gave the two MCG register configuration, pls follow up the state machine in the Figure 25-14. MCG mode state diagram to configure the MCG.

Hope it can help you.

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ryan

There are two possibilities for configuring the K24 for 120MHz PLL operation from a 16 MHz crystal (120MHz core, 60MHz bus, 24MHz flash, 40MHz FlexBus clock [some bits are optional or flags and don't directly influencing the frequency]):

1:

MCG_C2 = 0xa4;

MCG_C5 = 0x23;

MCG_C6 = 0x46;

SIM_CLKDIV1 = 0x01240000

MCG_C1 = 0x28

2:

MCG_C2 = 0xa0;

MCG_C5 = 0x25;

MCG_C6 = 0x55;

SIM_CLKDIV1 = 0x01240000

MCG_C1 = 0x28

The values that you have for SIM_CLKDIV1 look suspect since they would give 30MHz Flash and 60MHz FlexClock, which are both out or spec for the K24. This makes me believe that the setup must be for a lower core clock speed (such as 96Mhz) where they would be just in spec.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well my 10ms delays are 12.5ms but my 20ms delays are 20ms so the 2.5ms must just be some RTOS overhead. More importantly I am able to clock the USB with the PLL now so I'm relatively confident my settings are correct. Thank you again Mark.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

These are the values I went with.

#define CPU_MCG_C1_CONFIG_0 0x28U /* MCG_C1 */

#define CPU_MCG_C2_CONFIG_0 0x24U /* MCG_C2 */

#define CPU_MCG_C4_CONFIG_0 0x00U /* MCG_C4 */

#define CPU_MCG_C5_CONFIG_0 0x23U /* MCG_C5 */

#define CPU_MCG_C6_CONFIG_0 0x46U /* MCG_C6 */

#define CPU_MCG_SC_CONFIG_0 0x02U /* MCG_SC */

#define CPU_OSC_CR_CONFIG_0 0x80U /* OSC_CR */

#define CPU_SIM_SOPT1_CONFIG_0 0x00080000UL /* SIM_SOPT1 */

#define CPU_SIM_SOPT2_CONFIG_0 0x00010000UL /* SIM_SOPT2 */

#define CPU_SIM_CLKDIV1_CONFIG_0 0x01240000UL /* SIM_CLKDIV1 */

The MCG status register reads 0x6E after the configuration but my 10ms delay is still 12.5ms.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

is it just PRDIV0 and VDIV0 that set the PLL frequency? Just changing the macros to Mark's values still doesn't give me the right frequency. I'm using MQX to generate a 10ms delay and toggle a pin so I wouldn't expect it to be a perfect 10ms pulse but it should be close. Maybe its just my systick that's wrong. I guess if I'm changing PLL frequency the systick reload value has to change too.