- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Shape of single ended DDR3 clock

Shape of single ended DDR3 clock

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Shape of single ended DDR3 clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

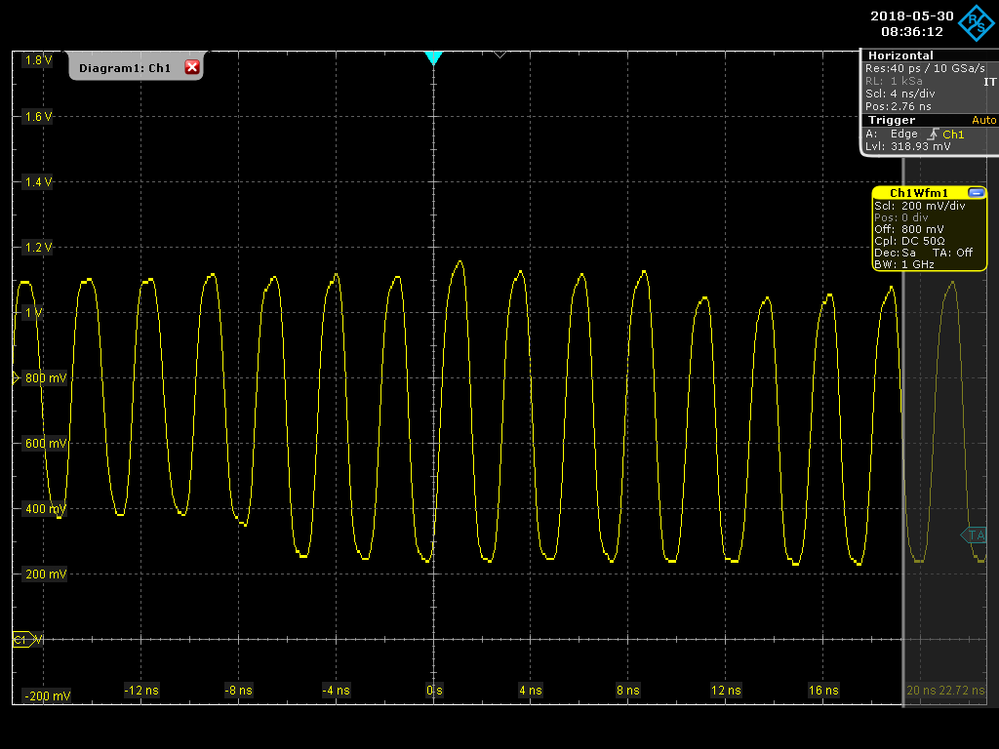

I have received the prototypes of a custom board I designed with an i.MX6ULL and DDR3L RAM. I use one 16-Bit RAM IC. I have finished calibrating the RAM and everything seems to run fine so far (tests in a climatic chamber are still to come). Now I measured the clock signal of the RAM to see if the termination is ok. In the picture I measured CLK_N to GND with an active probe. I am wondering why there is a change in the amplitude of the signal.

Everything seems to be within the allowed limits but I want to understand why the amplitude is changing like it is. Since this is the clock my understanding is that only the CPU is driving this signal, so I didn't expect to see something like this. In the design I use 100Ohm between the clk lines as termination. I do not use VTT termination. I measured this while running stress test tool v2.8.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Torben

amplitude change can be caused by variations NVCC_DRAM power supply.

General power and decoupling recommendations can be found in

Hardware Development Guide for the i.MX 6ULL Applications Processor

https://www.nxp.com/docs/en/user-guide/IMX6ULLHDG.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor

thanks for your answer. I followed the guide in the design but I will measure the voltage to be sure. I can see similar amplitude changes on the imx6ullevk board.

Update:

I measured NVCC_DRAM and there are no variations.