- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX8MQ EVK Configure Clock Frequency and Configure PLL

i.MX8MQ EVK Configure Clock Frequency and Configure PLL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX8MQ EVK Configure Clock Frequency and Configure PLL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How to configure clock frequency (NOC, AXI, AHB, CPU, DDRC) and configure PLL (ARM_A53_CLK, NOC_CLK, MAIN_AXI_CLK...)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi XIN

clocks are described in sect.5.1 Clock Control Module (CCM) i.MX8MDQ Reference Manual

https://www.nxp.com/docs/en/reference-manual/IMX8MDQLQRM.pdf

in uboot sources one can look at

imx-common\arm\arch - uboot-imx - i.MX U-Boot

imx8m_evk.c\imx8mq_evk\freescale\board - uboot-imx - i.MX U-Boot

in linux one needs to follow clock framework rules:

https://www.kernel.org/doc/Documentation/clk.txt

https://elinux.org/images/b/b8/Elc2013_Clement.pdf

clk-imx8mq.c\imx\clk\drivers - linux-imx - i.MX Linux kernel

fsl-imx8mq-evk.dts\freescale\dts\boot\arm64\arch - linux-imx - i.MX Linux kernel

use attached Porting Guide.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for your answer,

but there are several points to be confirmed. I hope you can answer it.

1. NOC,AXI,AHB clock configuration

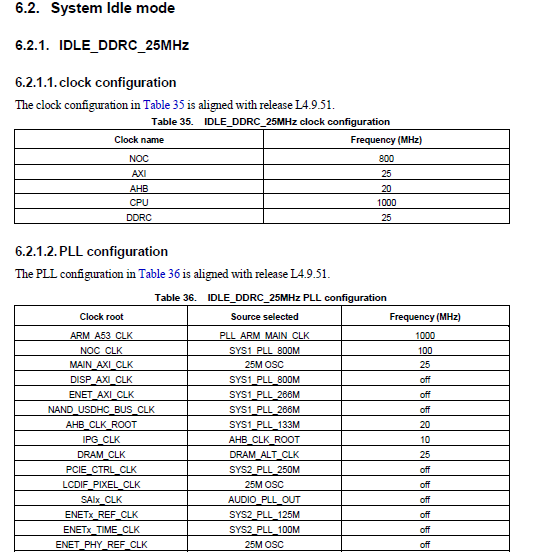

The document [i.MX 8M Quad Power Consumption Measurement] 6.2.1 IDLE_DDRC_25MHz

NOC,AXI,AHB clock configuration, call clk_set_rate function can be set?

For example: clk_set_rate (clks[IMX8MQ_NOC_CLK_DIV], 8000000000)

2. CPU Clock Configure

Use this command,Is it possible to meet the needs in 6.2.1.1 clock configuration

→ echo 1000000 > /sys/devices/system/cpu/cpu0/cpufreq/scaling_setspeed

3. DDRC Clock Configure

The ddrc clock frequency is 800MHz by default,If the ddrc clock is set to 25MHz

use this command?

→ echo mem > /sys/power/state

If use this command, all clocks and PLL turned off,NOC, AXI,AHB... will also be closed

Doing so does not satisfy the requirements in the table, right?,

How should the ddrc clock frequency be set?

4. PLL configuration

According to the “6.2.1.1 clock configuration” table below, how to set the PLL?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

suggest to create new threads for new questions.

~igor