- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Current limit function of LDO_1P1

Current limit function of LDO_1P1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello community,

About VDDHIGH_IN voltage of SABRE_SD i.MX6Q board,

It will dropped while wake from deep sleep mode.

(SABRE_SD_ILIMIT_disable_2P5_1P1_180518_224516_wakeup.png)

It seems that in-rush current to charge a bulk capacitor of NVCC_PLL_OUT.

So enabled current limit of LDO_1P1 by setting PMU_REG_1P1[ENABLE_ILIMIT] bit,

it seems that in-rush current is limited and voltage drop down has been resolved.

(SABRE_SD_ILIMIT_disable_2P5_enable_1P1_180518_225336_wakeup.png)

But lamp up of NVCC_PLL_OUT is slower than disable of current limit.

Is it OK to use a current limit function while wake up from deep sleep mode?

[Test environment]

Board : SABRE-SD i.MX6Q

OS : Linux BSP 4.9.11_1.0.0

Probe point :

ch1 : sh17 (VDDHIGH_IN)

ch2 : sh17 (VDDHIGH_IN)

ch3 : SW1_1 (CPUPWRON)

ch4 : R208 (NVCC_PLL_OUT)

Deep Sleep Mode :

Use a configuration of 5.2 Deep Sleep Mode (LPM6) in AN4509.

Best regards,

Ishii.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ishii

>VDDHIGH_IN voltage of SABRE_SD i.MX6Q board,

>It will dropped while wake from deep sleep mode

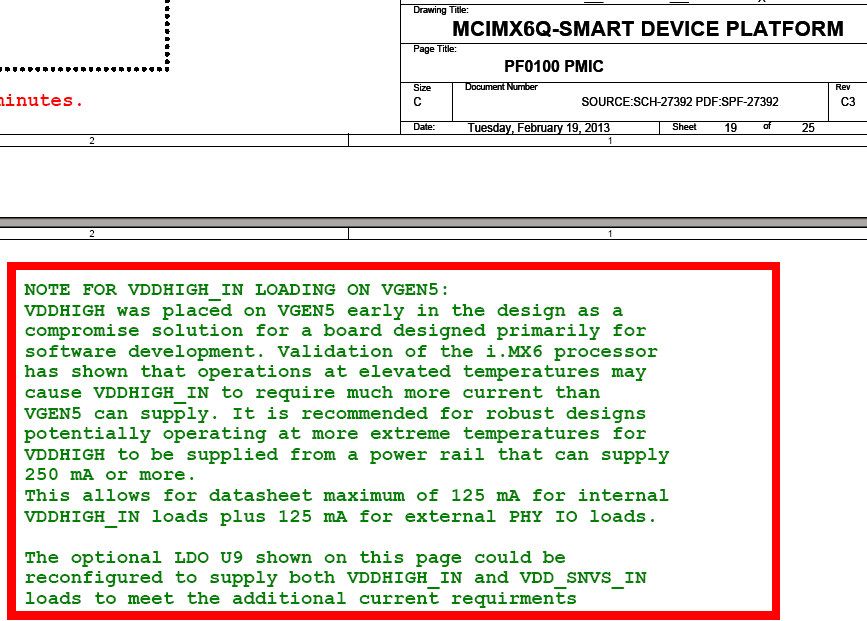

for VDDHIGH_IN voltage drop, may be useful to check comments on Sabre SD schematic

>Is it OK to use a current limit function while wake up from deep sleep mode?

yes, however additional time for slower ramp should be accounted in CCM_CLPCR

register STBY_COUNT settings, described in sect.18.6.18 CCM Low Power Control Register (CCM_CLPCR).

Procedure for exiting low power mode is described in sect.18.5.3.3.2 Exiting STOP

mode i.MX6DQ Reference Manual

https://www.nxp.com/docs/en/reference-manual/IMX6DQRM.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ishii

>VDDHIGH_IN voltage of SABRE_SD i.MX6Q board,

>It will dropped while wake from deep sleep mode

for VDDHIGH_IN voltage drop, may be useful to check comments on Sabre SD schematic

>Is it OK to use a current limit function while wake up from deep sleep mode?

yes, however additional time for slower ramp should be accounted in CCM_CLPCR

register STBY_COUNT settings, described in sect.18.6.18 CCM Low Power Control Register (CCM_CLPCR).

Procedure for exiting low power mode is described in sect.18.5.3.3.2 Exiting STOP

mode i.MX6DQ Reference Manual

https://www.nxp.com/docs/en/reference-manual/IMX6DQRM.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Thank you for your quick response.

By attached waveform, a time of NVCC_PLL_OUT that voltage is ready are almost 440usec.

If it must wait more than 440usec as examples,

CKIL = 32.768KHz => 30.5usec period

440usec / 30.5usec = 14.42

to wait more than equal 15CKIL clock cycle so,

CCM_CGPR[PMIC_DELAY_SCALER] = 0 // clock is not divided

CCM_CLPCR[STBY_COUNT] = 11b // CCM will wait (15*pmic_delay_scaler)+1 ckil clock cycles = 16 CKIL clock cycle

or

CCM_CGPR[PMIC_DELAY_SCALER] = 1 // clock is divided /8

CCM_CLPCR[STBY_COUNT] = 01b // CCM will wait (3*pmic_delay_scaler)+1 ckil clock cycles = 25 CKIL clock cycle

Is it correct?

By the way, I found that NVCC_PLL_OUT and VDDHIGH_CAP are used 22uF for SABRE-SD board.

But these are requested to connect 10uF or small one in IMX6DQ6SDLHDG.

It seems a root cause of VDDHIGH_IN voltage drop down.

Is it OK to use 22uF capacitor?

Best regards,

Ishii.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ishii

provided my answer was just general recommendation.

i.MX6Q Sabre SD board works well with NXP BSPs described on

It is not recommended to change software and hardware configuration

for NVCC_PLL_OUT, as these are verified and work fine.

If customer wishes to proceed with own configuration suggest to use help

with Professional Services to have more detailed analysis and verification:

http://www.nxp.com/support/nxp-professional-services:PROFESSIONAL-SERVICE

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Thank you for your answer.

I understand your suggestion.

We will introduce my customer to use professional support if they need more verification

about their custom setting.

Best regards,

Ishii.