- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Flexbus ALE

Flexbus ALE

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Flexbus ALE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I use 74LVC574A to latch address on Flexbus on rising edge of ALE signal. However latching (and thus my interface to SRAM) works only if I delay a little the ALE signal (the delay is achived by connecting 330 pF capacitor between ALE and GND). The problem is that the latch sometimes and on some address lines latch old value of address lines, because the change of the address happens with rising edge of ALE signal and the new address value is missed by a short moment.

So, is latching supposed to be working with ALE directly connected to CP pin of D flip-flop? If so, then there is something wrong with my PCB. My Address/data lines are directly connected to 4 components - MCU, latch, SRAM and CPLD (Altera MAX V). The length of the lines is 3 inch max. Maybe too much capacitance on these lines, which delays signal on address lines causing latch of old values?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Martin,

You did not mention the part number you are using, anyway, I suppose you use Kinetis for example K64.

Regarding your question, I suppose that the issue is related to the layout of the address lines, I give you two suggestions:

1)set the EXTS bit in FB_CSCRn, which will extend the address latch signal.

2)decrease the FlexBus clcok frequency. For example, the maximum FlexBus clock frequency is 50MHz for K64, if you reduce it to 25MHz, what is the result?

Hope it can help you

BR

Xiangjun Rong

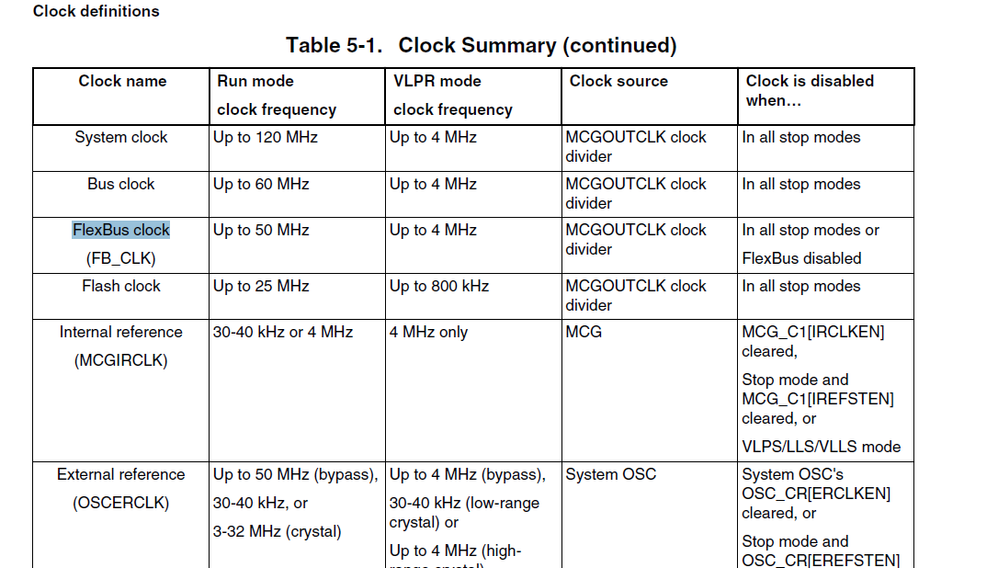

I post the clock distribution for K64:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiangjun,

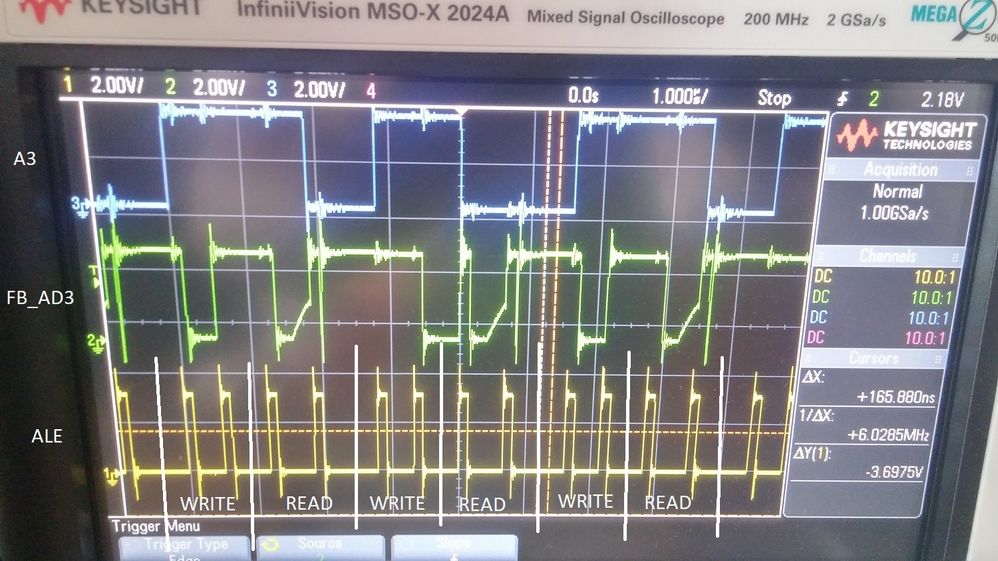

thanks for your reply. My part is MK22FN512VLL12. I divided Flexbus clock more, it is now 7,5 MHz. Still the same issue.

Without cap

Write/read to the same address with capacitor connected to ALE.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

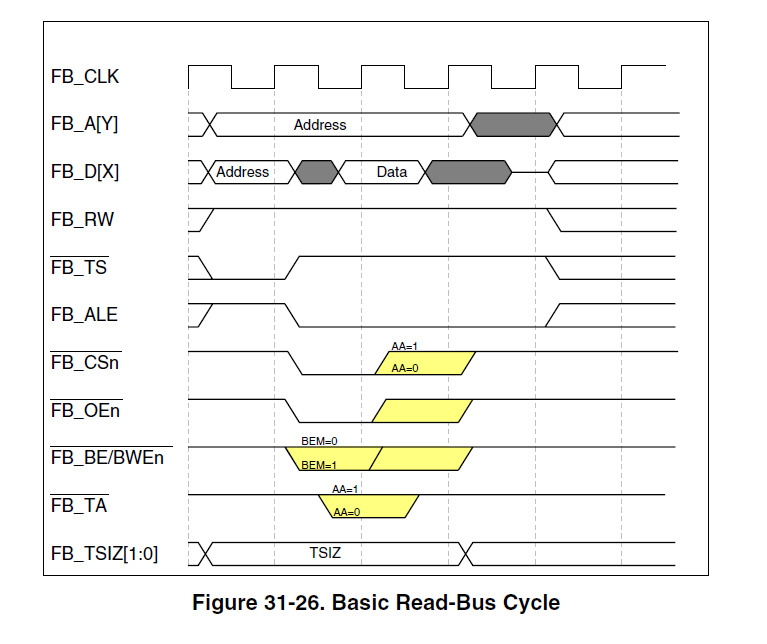

Hi, Martin,

It seems that you select wrong D-type flip-flop, the FB_ALE is falling-edge trigger rather than rising-edge trigger, but it seems that the 74LVC574A is rising-edge trigger, you have to select a D-type flip flop with falling edge trigger. Pls check yourself.

Hope it can help you.

BR

XiangJun Rong

FlexBus timing from RM of K22.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I noticed that ALE can be negated by setting FB_CSPMCR_GROUP1 = 2 (then you call the signal FB_TS) so there is no need to use falling edge triggered D flip flop. But still, the addres is not latched properly. I assume it is still the same problem - FB_TS rising edge and address lines deassert happens at the same moment.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

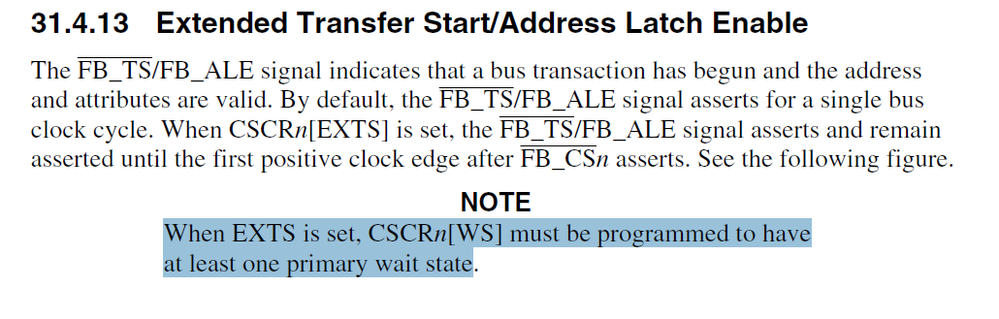

Hi, Martin,

Firstly, you are right that ALE can be negated by setting FB_CSPMCR_GROUP1 = 2 (then you call the signal FB_TS) so there is no need to use falling edge triggered D flip flop.

Have you tried to set the CSCRn[EXTS] = 1? There is a note that "When EXTS is set, CSCRn[WS] must be programmed to have

at least one primary wait state".

If the above solution is invalid, as you said that the address track on the PCB is too long.

BTW, try to reduce the FlexBus clock frequency and check the result.

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiangjun,

I already have 1 WS and I tried to set EXTS = 1 - it doesn't work. However, I'm not sure how prolonging the duration of address cycle can help. You write that the latching should occur on falling edge and there is no change in relation of falling edge and address presence on lines if I set EXTS to 1 or to 0.

I'm not electronics expert but I don't understand how latching address on Flexbus can work if edges of latching signal happen coincidentally with the change of the address to be latched. Is there a guarantee that the address is held on lines some time after falling edge of latching signal occurs (or is address present on lines some time before rising edge of latchin signal occurs)? At the moment I can't imagine how address latching on Flexbus can work without some additional circuitry added between MCU and the latch (in my case capacitor to delay the latching signal is sufficient).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I probably got it. There is FB_CSCR_ASET parameter that controls address setup time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, thanks. I will try falling edge latch or I will keep the cap on ALE line.

FYI Here, your colleague recommends 74lvc573a latch (latch on high value of ALE). I'm quite sure tthat here will be similar problem that I experience with D flip flop latching on rising edge.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The difference between the 573 and 574 is more than just which edge it clocks on.

The 573 is a a follow&hold device, while the 574 is a true D-Flip-Flop.