- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K148 time measuring using LPTMR

S32K148 time measuring using LPTMR

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm trying to configure the LPTMR module of S32K148 on our custom board to measure time between function calls StartTimeMeasurement and StopTimeMeasurement.

This is my configuration so far:

// Deactivates module clock before modification.

PCC->PCCn[PCC_LPTMR0_INDEX] &= PCC_PCCn_CGC_MASK;

// Sets SOSCDIV2_CLK as module clock source (we are using 8MHz crystal).

PCC->PCCn[PCC_LPTMR0_INDEX] &= PCC_PCCn_PCS_MASK;

PCC->PCCn[PCC_LPTMR0_INDEX] |= PCC_PCCn_PCS(1U);

// FRAC and PCD = 0. This should result in module input clock 8MHz.

PCC->PCCn[PCC_LPTMR0_INDEX] &= ~(PCC_PCCn_FRAC_MASK | PCC_PCCn_PCD_MASK);

// Reactivates module clock.

PCC->PCCn[PCC_LPTMR0_INDEX] |= PCC_PCCn_CGC(1U);

// Deactivates module before initialization.

LPTMR0->CSR &= ~LPTMR_CSR_TEN_MASK;

// Prescale Bypass - module clock source directly feeds the counter register. Set PCC_CLK as module source clock.

LPTMR0->PSR = LPTMR_PSR_PBYP(1U) | LPTMR_PSR_PCS(3U);

// Counter register counts to the highest possible value before generating interrupt.

LPTMR0->CMR = 0xFFFF;

// Sets module to function in the timer counter mode, counter register to clear when TCF is set and activates interrupt.

LPTMR0->CSR = LPTMR_CSR_TCF(1U) | LPTMR_CSR_TIE(1U) | LPTMR_CSR_TFC(0U) | LPTMR_CSR_TMS(0U);

// Activates module.

LPTMR0->CSR |= LPTMR_CSR_TEN(1U);

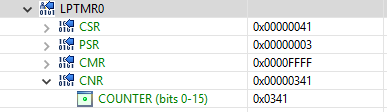

I see all the registers setup in the debugger, however the timer counter register value does not increment.

Thank you for any advice!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Tomas,

I have found the reason it returns 0.

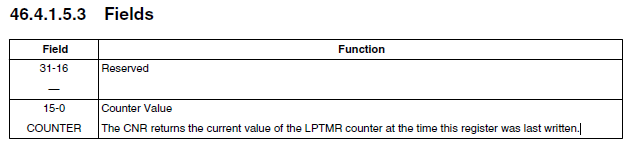

The CNR returns the current value of the LPTMR counter at the time this register was last written.

So, you need to write to the register first.

It will synchronize the register with the counter

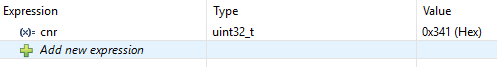

LPTMR0->CNR = 0x0001;

uint32_t cnr = LPTMR0->CNR;Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I don't see any problem in the code.

Please check if SOSC is enabled.

Have you tried with a different clock source?

The counter doesn't increment in when the core is halted.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Daniel,

Thank you for your reply. I already tried to switch from SOSCDIV2 to SPLLDIV2:

PCC->PCCn[PCC_LPTMR0_INDEX] &= PCC_PCCn_PCS_MASK;

PCC->PCCn[PCC_LPTMR0_INDEX] |= PCC_PCCn_PCS(6U);

However the counter still doesn't count (register CNR remailns 0x0). I know that both clocks SOSCDIV2 and SPLLDIV2 work as I'm already feeding them to CAN (SOSCDIV2) and CAN FD (SPLLDIV2) modules Protocol Engines in the same project and communication works.

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Tomas,

I have found the reason it returns 0.

The CNR returns the current value of the LPTMR counter at the time this register was last written.

So, you need to write to the register first.

It will synchronize the register with the counter

LPTMR0->CNR = 0x0001;

uint32_t cnr = LPTMR0->CNR;Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Daniel,

thank you, It works! Serves me right for not paying attention to the manual :smileyhappy:

Regards,

Tomas