- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K144 FLASH CACHE

S32K144 FLASH CACHE

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K144 FLASH CACHE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

At present I work on write to PFLASH and DFLASH memory. Im little confused about disabling flash cache. There is flash partitioning example in S32SDK_S32K14x_EAR_0.8.6 where is code disabling flash cache:

/* Disable cache to ensure that all flash operations will take effect instantly,

* this is device dependent */

#ifdef S32K144_SERIES

MSCM->OCMDR[0u] |= MSCM_OCMDR_OCM0(0xFu) | MSCM_OCMDR_OCM1(0xFu) | MSCM_OCMDR_OCM2(0xFu);

MSCM->OCMDR[1u] |= MSCM_OCMDR_OCM0(0xFu) | MSCM_OCMDR_OCM1(0xFu) | MSCM_OCMDR_OCM2(0xFu);

MSCM->OCMDR[2u] |= MSCM_OCMDR_OCM0(0xFu) | MSCM_OCMDR_OCM1(0xFu) | MSCM_OCMDR_OCM2(0xFu);

MSCM->OCMDR[3u] |= MSCM_OCMDR_OCM0(0xFu) | MSCM_OCMDR_OCM1(0xFu) | MSCM_OCMDR_OCM2(0xFu);

#endif /* S32K144_SERIES */

But in S32K-RM rev. 6 theres no bits OCM0, OCM2 for registers OCMDR[0], OCMDR[1] and any OCMx bits in OCMDr[2] and even register OCMDR[3]. OCM1 is 2bits wide, not 4bits like in axample above. Some of bits which is write in example is Reserved based on S32K-RM.

I think this code should look like this for S32K144:

#ifdef S32K144_SERIES

MSCM->OCMDR[0u] |= MSCM_OCMDR_OCM1(0x3u);

MSCM->OCMDR[1u] |= MSCM_OCMDR_OCM1(0x3u);

#endif /* S32K144_SERIES */

Please clarify how to disable cache for memories for S32K144 0N57u.

What are advandages/disadvantages for disabling cache when write/erase PFLASH, DFLASH and should be it disabled when I want for example update firmware by my custom bootloader?

Regards,

Arkadiusz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thank you for answer, but one more question, should I disable PFLASH and DFLASH cache if I want write only to DFLASH or just only DFLASH cache?

Regards,

Arkadiusz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,Arkadiusz,

Have you solved this problem?

I found that if i put this code in my project,the time of executing every line code will be slow when i use IAR compier.

#ifdef S32K146_SERIES

MSCM->OCMDR[0u] |= MSCM_OCMDR_OCM1(0xFu);

MSCM->OCMDR[1u] |= MSCM_OCMDR_OCM1(0xFu);

MSCM->OCMDR[2u] |= MSCM_OCMDR_OCM1(0xFu);

#endif /* S32K144_SERIES */

I really dont konw what does this code mean? i wonder that do i have to using this code to disable cache when write/erase PFLASH, DFLASH.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Arkadiusz,

There is no need to disable both if you modify only one of them.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Arkadiusz,

Thank you for the report, it has been forwarded to SDK design team and it will be fixed.

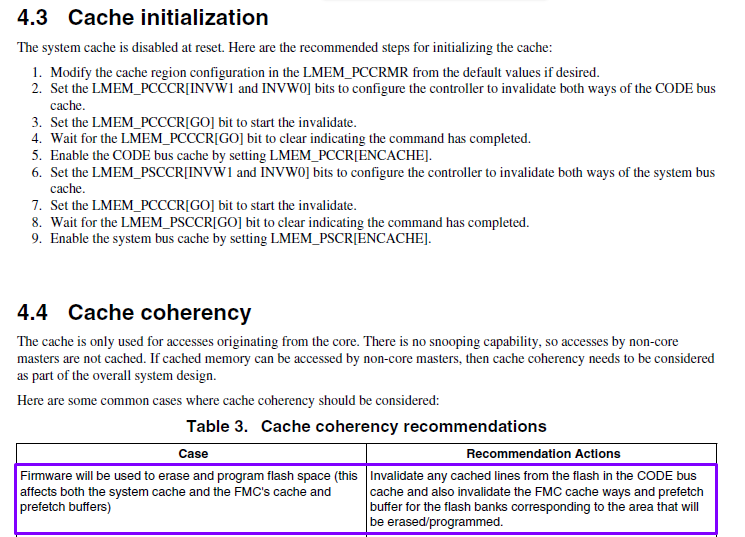

The cache should be disabled before modifying the flash content because the buffer is not updated automatically.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Which documents mentioned these "The cache should be disabled before modifying the flash content because the buffer is not updated automatically"?

Should i disable instruction cache before modifying corresponding flash content with the following statement?

LMEM->PCCCR = LMEM_PCCCR_INVW0(1) | LMEM_PCCCR_INVW1(1) | LMEM_PCCCR_GO(1);

Thanks.

Regards,

Liu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Liu,

This is not explicitly required but recommended, this is on the user's responsibility.

You could refer to AN4745 Optimizing Performance on Kinetis K-series MCUs

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniel,

Thanks for your reply.

Regards,

Liu