- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- DEVKIT-S12G128 PWM

DEVKIT-S12G128 PWM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DEVKIT-S12G128 PWM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a DEVKIT-S12G128, 8Mhz crystal. CodeWarrior 5.9.0. The issue I have is with the PWM. I have setup a 24Mhz bus clock and a 24kHz PWM (16bit) channel (10%duty) . Everything looks ok if you look at a few cycles of the PWM. After about 230ms the output STOPS and restarts in another 230ms.

//---------------------------------

// example devkit-s12g128 with 8MHz crystal

// output on pin PP1 (J2-01)

//

// 24khz pwm signal with a 10% duty cycle.

// After about 230ms the output STOPS. It restarts after about 230ms.

//

// At 1% duty the output stops after 22ms. It restarts after about 440ms

#include <hidef.h>

#include "derivative.h"

void SetPEEmodeBUSCLK(byte _synr, byte _refdv, byte _postdiv);

void main(void)

{

ECLKCTL_NECLK = 0;

DDRP =0x02;

SetPEEmodeBUSCLK(0x02, 0x80, 0x00); // 24MHz BUSCLK from 8 MHZ oscclk, PEE mode

//------------------------------------------------

PWME = 0x00; // Disable all PWM channels

PWMPOL =0xFF; // All channels are high an go low

PWMCLK = 0x00; // All channels are clocked from A or B clock source

PWMCLKAB = 0x00; // Clock A is the source clock for all channels

PWMPRCLK = 0x00; // Clock A & B equal to BUS clock

PWMCAE = 0x00; // left aligned

PWMCTL = 0x10; // 0-1 concatenated to form 16-bit PWM

PWMPER01 = 1000; // PWM channel 01 period

PWME = 0x02; // Enable the channel

PWMDTY01 = 100; // set duty cycle for 01

//-------------------------------------------------

for(;;)

{

_FEED_COP();

}

}

void SetPEEmodeBUSCLK(byte _synr, byte _refdv, byte _postdiv)

{

CPMUSYNR = _synr;

CPMUREFDIV = _refdv;

CPMUPOSTDIV = _postdiv;

CPMUOSC_OSCE = 1; //enable external oscillator OSCE

while(!CPMUFLG_UPOSC)

{// you can check for timeot here with error message report

};

while(!CPMUFLG_LOCK)

{// you can check for timeot here with error message report

};

//--- select clocks --------------------

CPMUCLKS = 0B10000011; // bus=fPLL/2; COP is clocked from OSCCLK

if(CPMUCLKS != 0B10000011) // After writing CPMUCLKS register, it is strongly recommended to read

{ // back CPMUCLKS register to make sure that write of PLLSEL,

asm nop; // RTIOSCSEL, COPOSCSEL0 and COPOSCSEL1 was successful.

}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Daniel

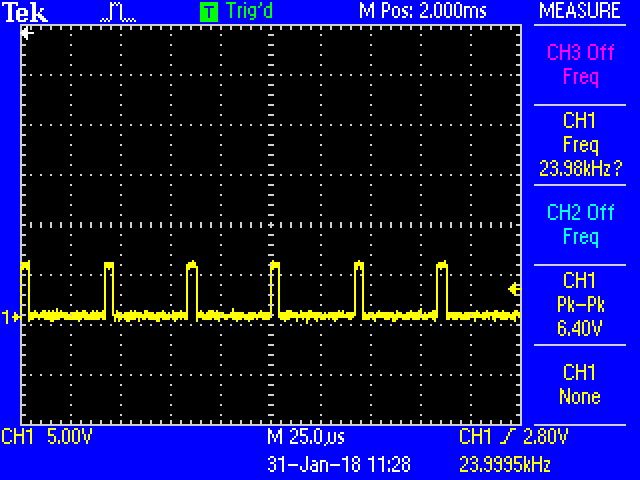

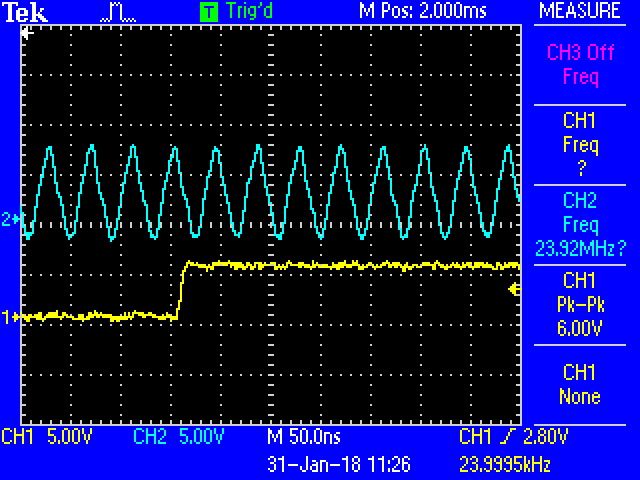

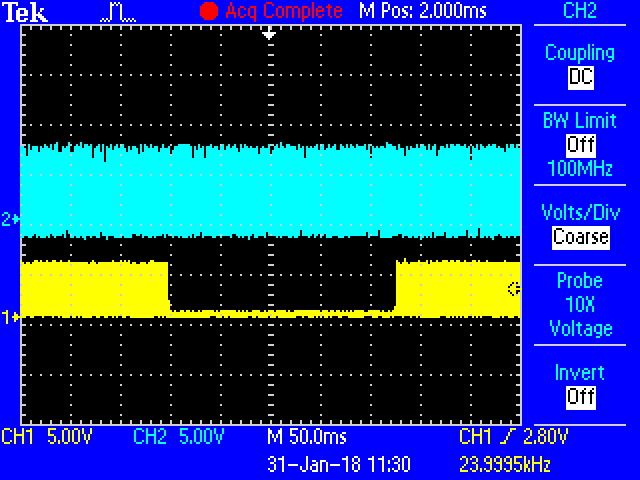

I have monitored ECLK it looks fine. The board does not restart. Here are a few scope plots.

Robert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robert,

Thank you for the plots.

Have you tried running only the code you posted?

The PWM1 function of PP1 has highest priority, so the PWM module controls the pin if enabled.

Unless it is embedded in a project where you could accidently disable the PWM.

Could you halt the program when the PWM is stopped and check all PWM registers?

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Daniel

That is all the code. I have reloaded all the pwm registers in the main loop and that did not work either. I don't know how to halt the code when the PWM is stopped.

One note the code runs if I don't use the PLL. I need the fast/more accurate clock for my project.

I have mask 0N51A

Robert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robert,

I have just run the code on TWR-S12G128 and everything works. It doesn't stop.

Could you monitor BUS clock on ECLK?

Regards,

Daniel