- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Model-Based Design Toolbox (MBDT)

- :

- Model-Based Design Toolbox (MBDT)

- :

- modify the .lcf file and .tmf file result the program can not run

modify the .lcf file and .tmf file result the program can not run

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

modify the .lcf file and .tmf file result the program can not run

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

Now I use the MCToolbox with MPC5643L.In the model I use FlexPWM without any modify,the program can run.When I modify the rappid_564xl_cw_flash_2013.tmf and the MPC564xLFLASH.lcf,the program can not run.

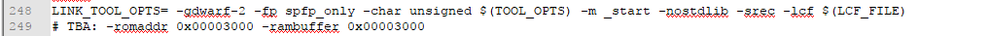

In the rappid_564xl_cw_flash_2013.tmf file,I modify in the below:

In the file I delete the '-romaddr 0x00003000 -rambuffer 0x00003000'.

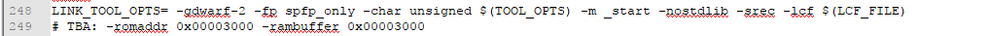

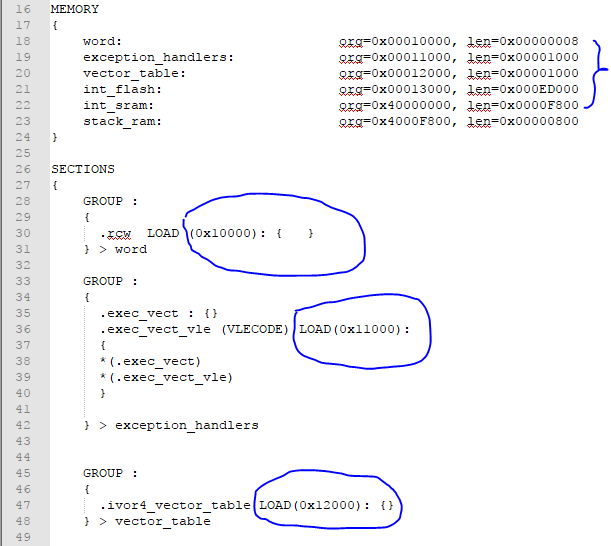

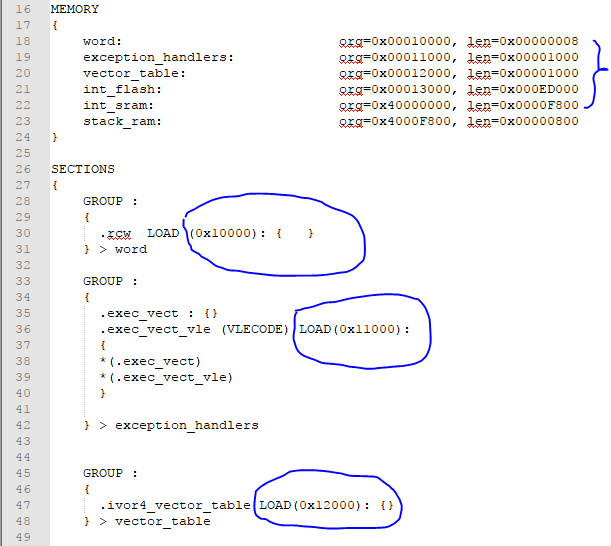

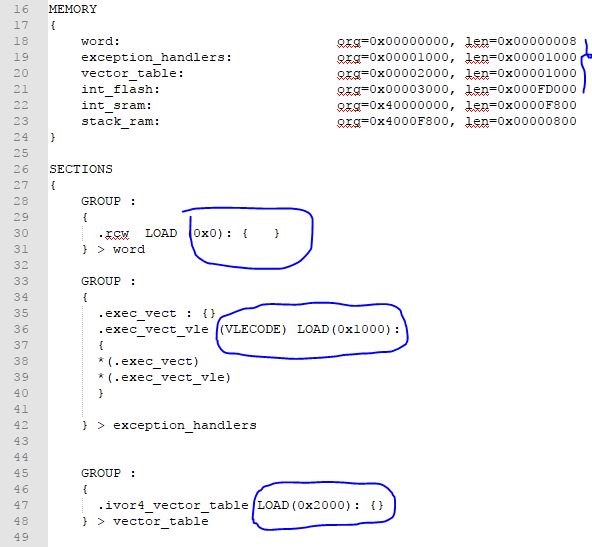

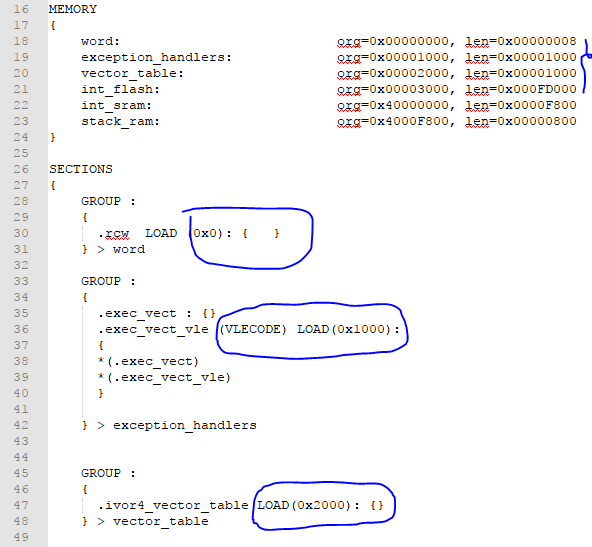

In the MPC564xLFLASH.lcf file,I modify in the below:

In the modify file:

the old .lcf file

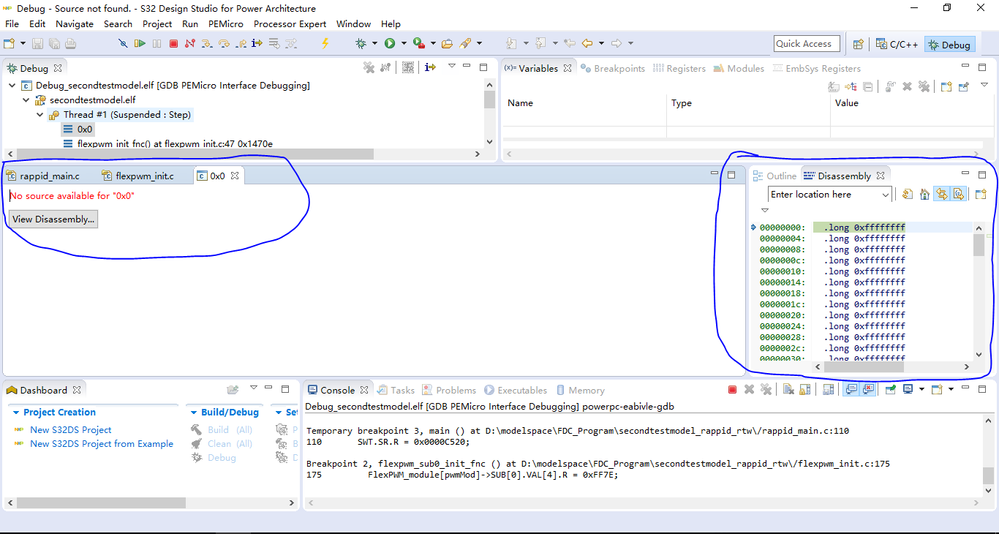

After I build the model,I debug the program by S32DS.

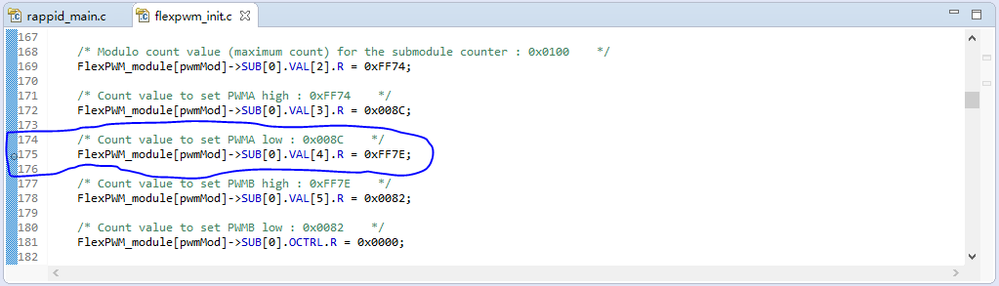

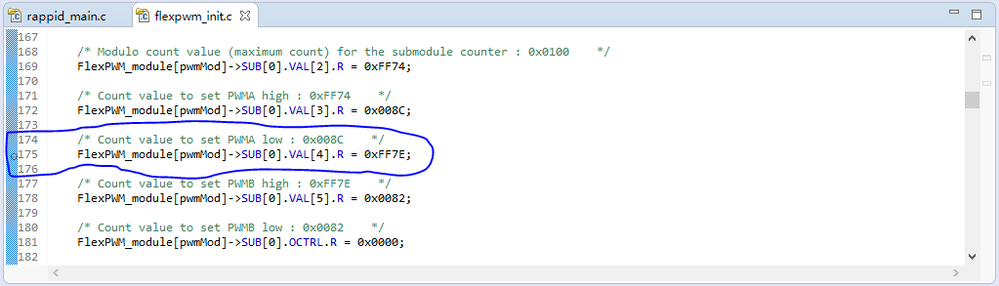

First I set breakpoint in the below:

In the debug process.First I click the run button, the program go to the bteakpoint.Second I click 'Step over' button twice,the program only run one step and in the next step the program run to the 0x0.

I do not know how to solve the problem,can you help me?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi hongjinzeng,

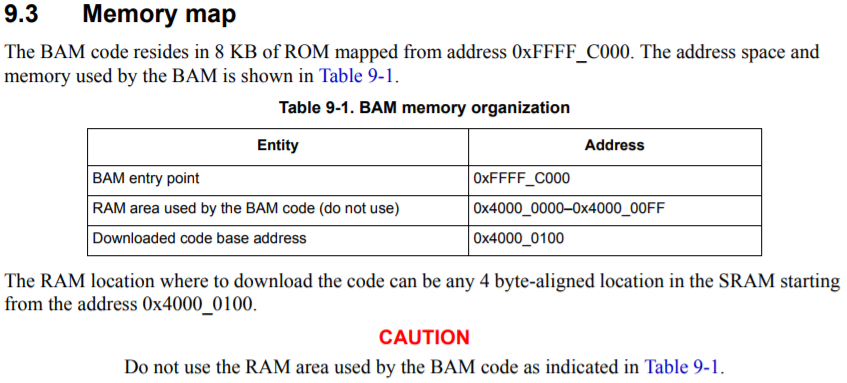

I checked your project and it looks like you are placing data over a data section that is exclusively used by the Boot Assist Module (BAM)

In your map file is see:

.data section layout

Starting Virtual File

address Size address offset

---------------------------------

00000000 000020 40000000 00003ca0 1 .data adc_564xl_library.o

00000000 000020 40000000 00003ca0 8 @LOCAL@adc_pin_init__FUcUc@adc_ch2num adc_564xl_library.o

00000020 000018 40000020 00003cc0 1 .data freemaster_protocol.o

00000020 000018 40000020 00003cc0 8 @139 freemaster_protocol.o

.sdata section layout

Starting Virtual File

address Size address offset

---------------------------------

00000000 000009 40000038 00003cd8 1 .sdata secondtestmodel.o

00000000 000004 40000038 00003cd8 4 DutyCycle secondtestmodel.o

00000004 000004 4000003c 00003cdc 4 Frequency secondtestmodel.o

00000008 000001 40000040 00003ce0 1 IGBTEn secondtestmodel.o

00000009 000007 40000048 00003ce8 8 *fill*

00000010 000010 40000048 00003ce8 1 .sdata FlexPWM_564xL_library.o

00000010 000004 40000048 00003ce8 4 sysClk FlexPWM_564xL_library.o

00000018 000008 40000050 00003cf0 8 FlexPWM_module FlexPWM_564xL_library.o

00000020 000008 40000058 00003cf8 1 .sdata adc_564xl_library.o

00000020 000008 40000058 00003cf8 8 ADC adc_564xl_library.o

00000028 000008 40000060 00003d00 1 .sdata flexpwm_init.o

00000028 000008 40000060 00003d00 8 FlexPWM_module flexpwm_init.o

.sbss section layout

Starting Virtual File

address Size address offset

---------------------------------

00000000 000009 40000068 00003d08 1 .sbss freemaster_appcmd.o

00000000 000004 40000068 00003d08 4 pcm_pAppCmdCallId freemaster_appcmd.o

00000004 000001 4000006c 00003d0c 1 pcm_nAppCmdResultDataLen freemaster_appcmd.o

00000005 000001 4000006d 00003d0d 1 pcm_nAppCmdResult freemaster_appcmd.o

00000006 000002 4000006e 00003d0e 2 pcm_nAppCmdLen freemaster_appcmd.o

00000008 000001 40000070 00003d10 1 pcm_nAppCmd freemaster_appcmd.o

00000009 000007 40000078 00003d18 8 *fill*

00000010 00003a 40000078 00003d18 1 .sbss freemaster_rec.o

00000010 000004 40000078 00003d18 4 pcm_pCompareFunc freemaster_rec.o

00000014 000004 4000007c 00003d1c 4 pcm_nRecBuffAddr freemaster_rec.o

00000018 000004 40000080 00003d20 4 pcm_uTrgThreshold freemaster_rec.o

0000001c 000001 40000084 00003d24 1 pcm_bTrgVarSigned freemaster_rec.o

0000001d 000001 40000085 00003d25 1 pcm_nTrgVarSize freemaster_rec.o

00000020 000004 40000088 00003d28 4 pcm_nTrgVarAddr freemaster_rec.o

00000024 000004 4000008c 00003d2c 4 pcm_dwRecEndBuffPtr freemaster_rec.o

00000028 000004 40000090 00003d30 4 pcm_dwRecWritePtr freemaster_rec.o

0000002c 000002 40000094 00003d34 2 pcm_wRecBuffStartIx freemaster_rec.o

00000030 000004 40000098 00003d38 4 pcm_wRecFlags freemaster_rec.o

00000034 000002 4000009c 00003d3c 2 pcm_wStoprecCountDown freemaster_rec.o

00000036 000002 4000009e 00003d3e 2 pcm_wRecTimeDivCtr freemaster_rec.o

00000038 000008 400000a0 00003d40 8 pcm_pRecVarSize freemaster_rec.o

00000040 000001 400000a8 00003d48 1 pcm_nRecVarCount freemaster_rec.o

00000042 000002 400000aa 00003d4a 2 pcm_wRecTimeDiv freemaster_rec.o

00000044 000001 400000ac 00003d4c 1 pcm_nRecTriggerMode freemaster_rec.o

00000046 000002 400000ae 00003d4e 2 pcm_wRecPostTrigger freemaster_rec.o

00000048 000002 400000b0 00003d50 2 pcm_wRecTotalSmps freemaster_rec.o

0000004a 000006 400000b8 00003d58 8 *fill*

00000050 000009 400000b8 00003d58 1 .sbss freemaster_scope.o

00000050 000008 400000b8 00003d58 8 pcm_pScopeVarSize freemaster_scope.o

00000058 000001 400000c0 00003d60 1 pcm_nScopeVarCount freemaster_scope.o

00000059 000007 400000c8 00003d68 8 *fill*

00000060 000014 400000c8 00003d68 1 .sbss freemaster_serial.o

00000060 000001 400000c8 00003d68 1 pcm_nRxCheckSum freemaster_serial.o

00000064 000004 400000cc 00003d6c 4 pcm_pRxBuff freemaster_serial.o

00000068 000004 400000d0 00003d70 4 pcm_pTxBuff freemaster_serial.o

0000006c 000001 400000d4 00003d74 1 pcm_nRxTodo freemaster_serial.o

0000006d 000001 400000d5 00003d75 1 pcm_nTxTodo freemaster_serial.o

00000070 000004 400000d8 00003d78 4 pcm_wFlags freemaster_serial.o

.bss section layout

Starting Virtual File

address Size address offset

---------------------------------

00000000 000026 400000e0 00003d08 1 .bss secondtestmodel.o

00000000 000012 400000e0 00003d08 4 secondtestmodel_B secondtestmodel.o

00000014 000012 400000f4 00003d1c 4 secondtestmodel_Y secondtestmodel.o

I'm not an expert in how this processor works but i think that might be a potential culprit for the S32DS behavior you are seeing with 0x0 jump.

So, for the Simulink model settings i see no issues - the only questionable thing is the linker command file mapping. My advice is to get in touch with https://community.nxp.com/community/s32/mpc5xxx community since there are experts in MPC series. I think at this point is just a matter of setting the memory map correctly according with MCP5643L restrictions (which unfortunately i'm not fully aware off)

Hope this helps!

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi popa,

Thank you for your reply.Should I ask the question in MPC5XXX community?Or can you help me ask the MPC5xxx community?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My suggestion is to ask on MPC5xxx community directly and provide just the CodeWarrior project you are using. There is no direct cross-reference between communities, the persons that are visiting that space might be totally different than the ones interested in Model-Based Design Tools community.

In my opinion - your question have more chances of being solved there since it is about setting up a custom project. It does not matter how the C-code was generated (manually of automatically). You also proved that is works with default memory layout - so it should be straightforward for someone who has knowledge on MPC5xxx.

Also, in that community i see there are a couple of issues related with custom boot-loaders for such processors.

Best regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi hongjin zeng,

Can you tell us what are you trying to achieve ?

Why do you need to change the default memory layout ?

Thank you!

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi popa,

Can you help me solve the problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to write a CAN flash bootloader,so in the application software the memory layout need to modify.