- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- K61 HS USB with cache enabled

K61 HS USB with cache enabled

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using HS USB on a Mk61FN1M0VMJ12 MCU. My code is working when the cache is disabled, but not when it is enabled. Is there some interaction between the cache and HS USB peripheral?

Thanks in advance :smileyhappy:

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am still enable to run the HSUSB with descriptors located in a cached memory region.

However I have improved my situation by using a two DDR regions, one cached and the other non-cached.

I enable caching in region 8 and disable caching in region 7, the aliased address

I am linking the HSUSB descriptors in the cached DDR system section (0x8xxxxxxx) then adjusting the addresses to the aliased, non-cached DDR section (0x7xxxxxxx) by subtracting 0x10000000.

This solution seems to work well.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have continued to debug this issue. I've found that in order to use HSUSB with the DDR region cache R8 enabled I needed to move the HSUSB endpoint descriptors, transfer descriptors and buffers to SRAM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

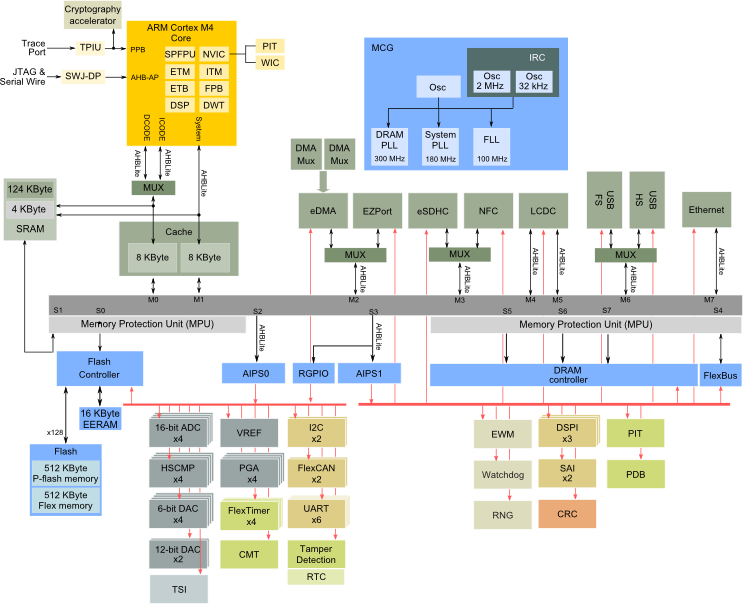

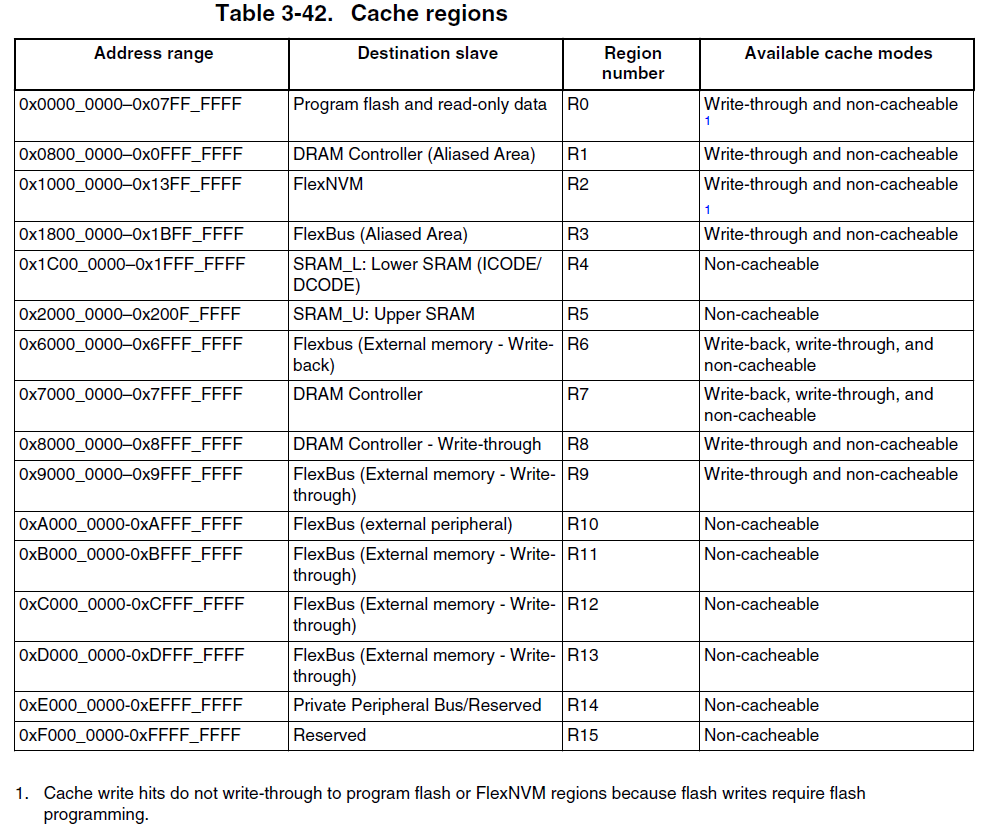

Hi @mrharmonsr ,

I think the K61 block diagram below will help explain what you are seeing. The system cache is used on the two master busses from the Cortex-M4 core, called SYSTEM and CODE bus. Accesses from the other crossbar masters, like the High-Speed USB, do not interact with the cache. When using RAM that is shared between multiple masters, like the USB buffers and descriptors, that RAM should not be cached. The internal SRAM is an ideal location for the USB memory, as it is tightly coupled to the core, so doesn’t benefit from cache, and is accessible by other masters. If you prefer to use external RAM for shared memory, then you can configure a cache region for non-cacheable. Based on the memory map, you can use different cache policies for different cache regions, and divide your DRAM up between cacheable and non-cacheable regions. See Cache Regions table below from the reference manual. For more details on configuring a cache region as non-cacheable, refer to the LMEM_PCCRMR register in the Local Memory Controller chapter of the reference manual. Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am still enable to run the HSUSB with descriptors located in a cached memory region.

However I have improved my situation by using a two DDR regions, one cached and the other non-cached.

I enable caching in region 8 and disable caching in region 7, the aliased address

I am linking the HSUSB descriptors in the cached DDR system section (0x8xxxxxxx) then adjusting the addresses to the aliased, non-cached DDR section (0x7xxxxxxx) by subtracting 0x10000000.

This solution seems to work well.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Larry,

there isn't a word said that HS USB is conflict with cache. When you use HS USB, you should only close MPU.

Regards

Jing