- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- How can Cortext-M4 of imx6sx access FPGA by eim

How can Cortext-M4 of imx6sx access FPGA by eim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How can Cortext-M4 of imx6sx access FPGA by eim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,all

I have a imx6sx-sdb board,how can the M4 access FPGA by EIM ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

the problem has been solved!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jingyang

m4 can use eim in the same manner as a9, only

from m4 side module addresses can be different, use Table 2-2. CM4

memory map i.MX6SX Reference Manual

http://www.nxp.com/docs/en/reference-manual/IMX6SXRM.pdf

dts file with eim

linux-imx.git - i.MX Linux Kernel

modules which may conflict with eim should be disabled in a9 dts

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,igor

I want both a9 and M4 can access fpga,can this do?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

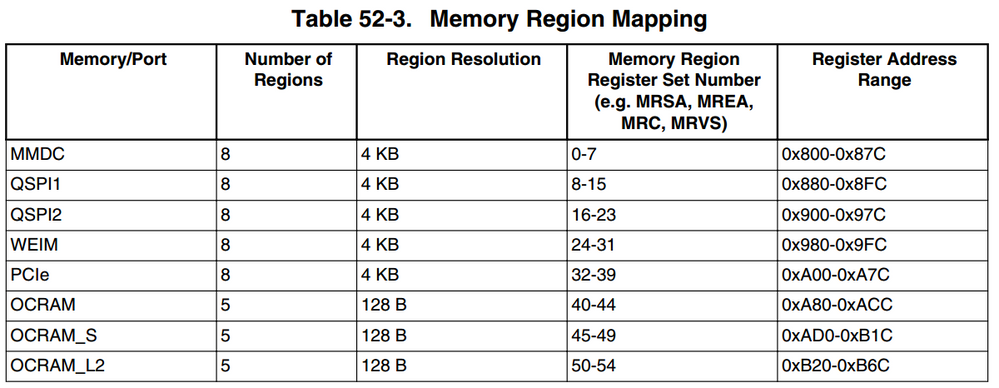

yes it is possible, please check permissions defined in

rdc, described in Chapter 52 Resource Domain Controller (RDC)

i.MX6SX Reference Manual.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,igor

what the address I can use to access EIM on M4,when on A9,I can use mmap() to map the 0x50000000(EIM addr) to 0(virtual addr),how can this do on M4?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

one can look at m4 qspi examples in i.MX7D FreeRTOS, for eim this

should be the same only with different addresses

Board Support Packages (3)

FreeRTOS_iMX7D_1.0.1_LINUX

https://www.nxp.com/products/processors-and-microcontrollers/applications-processors/i.mx-applicatio...

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,igor

does this mean that the EIM should be enabled in uboot?the qspi examples in i.MX7D FreeRTOS say that " To start this demo, the QSPI Flash in U-Boot should be enabled." if so ,I should configure EIM pins and clock in uboot? that's very strange,I think M4 can access EIM not only in uboot system startup,is this right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

you are right eim can be configured later, in linux.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,igor

I'm a little confused. Is there any specific solution for M4 accessing EIM? For example, like A9, first configuring the pin function, then configuring the clock, configuring control registers (EIM_CSnGCR1, EIM_CSnGCR2, EIM_CSnRCR1...), and finally making memory mapping (mmap) to access EIM.

17702710280@163.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,igor

I have read the 6sx RM,I have some questions:

what does this mean? and does it have anything to do with EIM memory (0x50000000-0x57FFFFFF)?

If I want use function(RDC_SetMrAccess(RDC_Type * base, uint32_t mr, uint32_t startAddr, uint32_t endAddr,

uint8_t perm, bool enable, bool lock) on M4 to access EIM(FPGA),how can I choose the startAddr and endAddr?