- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- How can I define the lcdif_modedb ??

How can I define the lcdif_modedb ??

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How can I define the lcdif_modedb ??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I testing the LCD output but I cannot see a perfect and clear output yet.

My First Question was this : ADV7125 with Imx6 is not working normally

I found out DISP0_DAT16~DISP0_DAT23 was not set normally.

So I can see red color now.

But I cannot calculate the correct timing for my resolution.

I wanna set the my frame buffer to 640x480, 60Hz, RGB24, bpp=32.

I set the lcdif_modedb like this :

{

"640x480", // name

60, // refresh

640, // xres

480, // yres

39721, // pixclock

16, // left margin (HBP) Back Porch

48, // right margin (HFP) Front Porch

2, // upper margin (VBP) Back Porch

25, // lower margin (VFP) Front Porch

96, // Hsync Length

2, // VSync Length

FB_SYNC_CLK_LAT_FALL, // Sync

FB_VMODE_NONINTERLACED, // Vmode

0,},

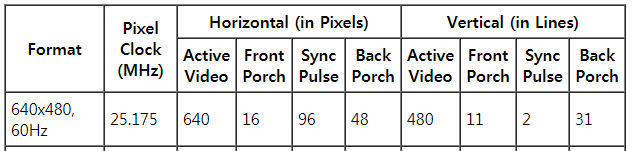

Actually, I refer from below data. from googling.

But this make shifted output.

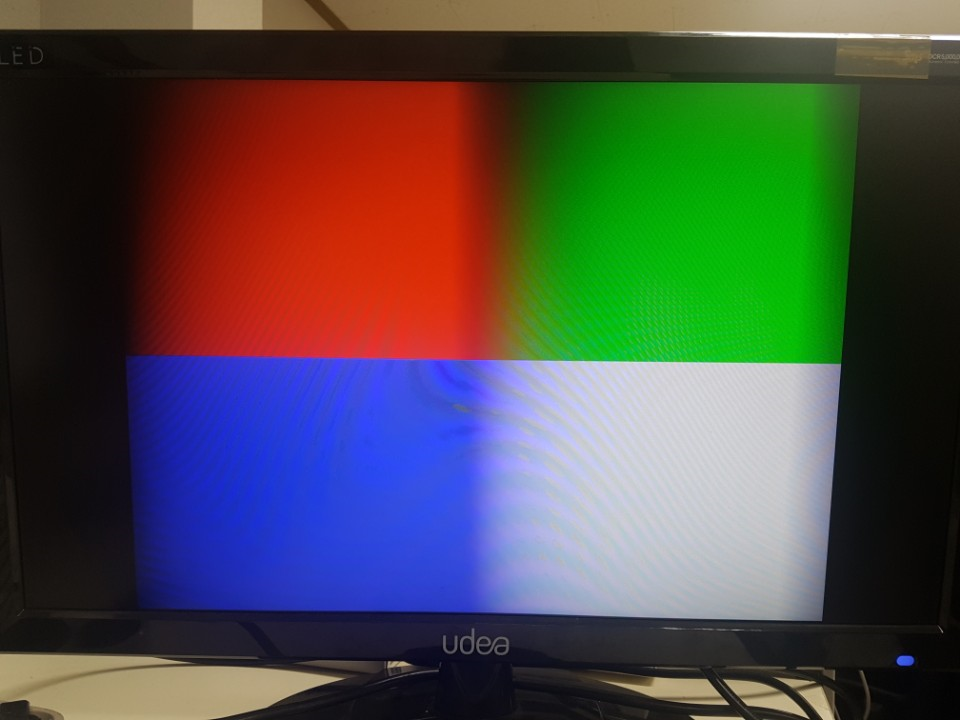

My upper setting value makes better output. Like this :

This Image is 4 seperated color that (R 255), (G 255), (B 255), (R255G255B255).

Red and green, blue and white's boarder line looks like gradation.

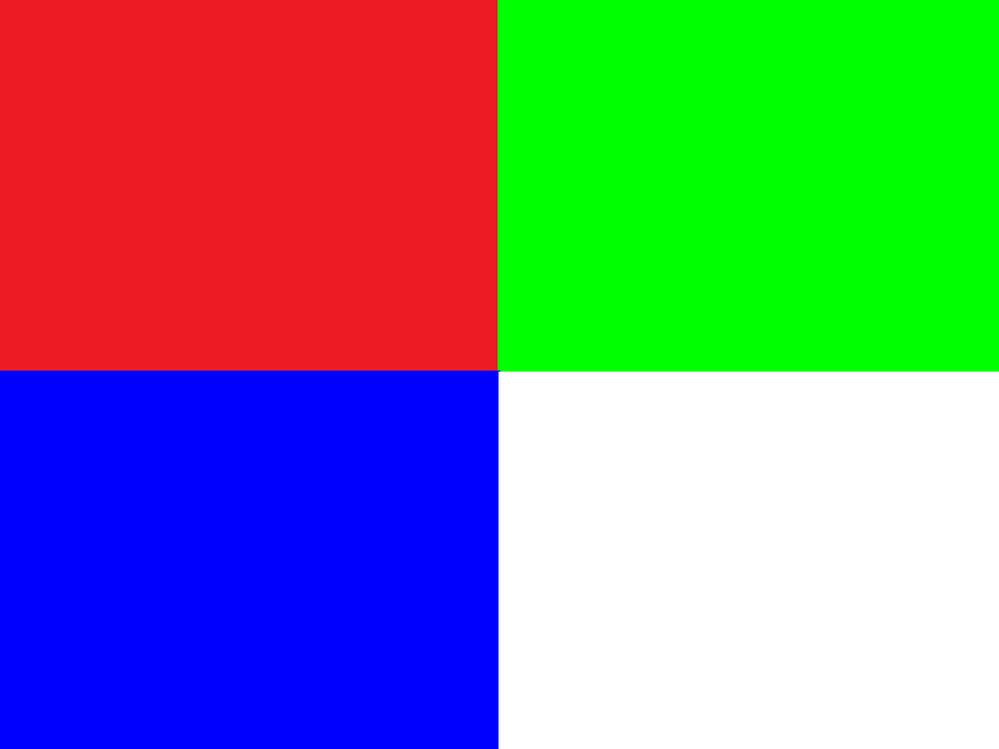

My original image is this : (640 x 480)

At this time, fbset's result is

mode "640x480-62"

# D: 25.176 MHz, H: 31.469 kHz, V: 61.826 Hz

geometry 640 480 640 480 32

timings 39721 16 48 2 25 96 2

rgba 8/16,8/8,8/0,8/24

endmode

PCLK and VSYNC is holded.

but HSYNC looks like jitter. (little bit.. shaking..)

I cannot understand..

So I tried another timing and resolution.

I setted

{

"1280x960", // name

60, // refresh

1280, // xres

960, // yres

9794, // pixclock

216, // left margin (HBP) Back Porch

80, // right margin (HFP) Front Porch

30, // upper margin (VBP) Back Porch

1, // lower margin (VFP) Front Porch

136, // Hsync Length

3, // VSync Length

FB_SYNC_CLK_LAT_FALL, // Sync

FB_VMODE_NONINTERLACED, // Vmode

0,},

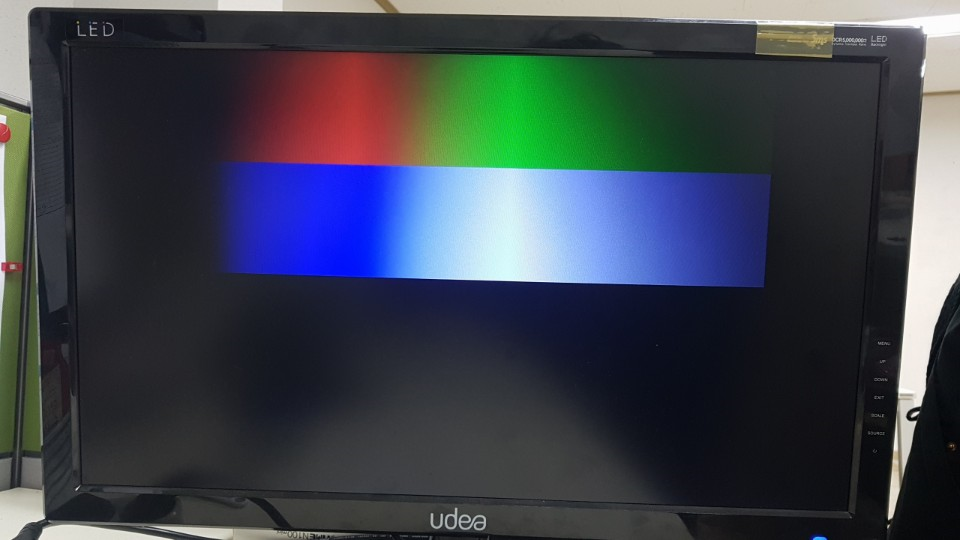

And result is

Image size is 640x480 and resolution is 1280x960

so, I understood height is half.

but I cannot understand why width is not half..

Most of all,

Left and middle's border line looks like blur and gradation..

How can I found the exact timing for 640 480 resolution?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This problem is not caused by timing..

It was solved by remove the RGB capacitor.. lol.....

Thank you for your concern of my problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi 호영 노

according to example in datasheet ADV7125 on p.13 : "Dot Rate = 1024 × 1024 × 60/0.8 = 78.6 MHz"

http://www.analog.com/media/en/technical-documentation/data-sheets/ADV7125.pdf

so for pixel clock one can try: 640x480x60/0.8=23.040MHz

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for reply.

I tried, but nothing changed,

{

"LCD-720P", // name

60, // refresh

640, // xres

480, // yres

43402, // pixclock

48, // left margin (HBP) Back Porch

16, // right margin (HFP) Front Porch

2, // upper margin (VBP) Back Porch

11, // lower margin (VFP) Front Porch

96, // Hsync Length

2, // VSync Length

FB_SYNC_CLK_LAT_FALL, // Sync

FB_VMODE_NONINTERLACED, // Vmode

0,},

// fbset Data :

mode "640x480-58"

# D: 23.040 MHz, H: 28.801 kHz, V: 58.183 Hz

geometry 640 480 640 480 32

timings 43402 48 16 2 11 96 2

rgba 8/16,8/8,8/0,8/24

endmode

Could you tell me how can I determine the "Retrace Factor" ?

I think that datasheet's 0.8 is just example.

So I think that we have to find exact value.

(Should I adjust another timings value? ex) front porch, back porch etc..)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

for linux fb_mode settings one can look at sect.2.4.1 Timing Concepts AN3974

https://www.nxp.com/docs/en/application-note/AN3974.pdf

pixel clock calculations example:

https://community.nxp.com/thread/308170#comment-422519

Best regards

igor