- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- eTimer oflag question

eTimer oflag question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

eTimer oflag question

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I meet some question about eTimer module in mpc57xx mcu ,In the compare registor and oflag operate chapter show oflag state can only change state after count reach compare value.

I want make eTimer1_ETC5 io output an square wave in countine counter mode,

So i set eTimer1_ETC5 io as eTimer input/output functon,eTimer as counter mode ,every 10ms toggle oflag state,but i capture eTimer1_ETC5 output waveform is noncorrect. waveform period is 20ms is right,but waveform voltage just 1.2V and it shape is not a square waveform.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i want to use eTimer create an event to triggle adc convert,how should i do.

I need to connect eTimer output with adc channel?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

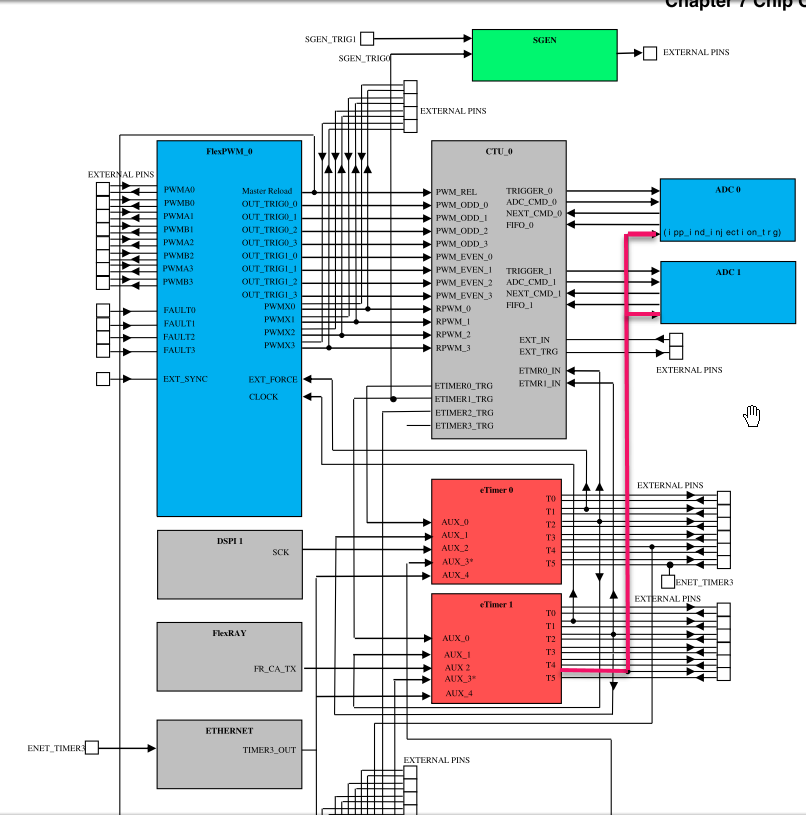

The ADC can be directly triggered from eTimer output, usually the channel 5 is used for this purpose.

Below is internal connection of the MPC5744P

The ADC must enable external trigger and injected conversion.

Attached you have an example which shows ADC triggering from the eTimer1 module.

The OFLAG signal from the eTimer1 channel 5 is fed into ADC, and so ADC is set up for injected conversion with end of scan interrupt. Example was done for MPC5604P, but the modules are similar.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

I have some question about adc triggle dma transfer. ADC0 module is configure to one_shot conversion and adc0-ch7 ,adc0-ch8 is enable ,throughout set start flag triggle adc conversion.

when ch7 and ch8 has an eoc condition to triggle dma transfer.

uint32_t adc0ChannelData[64] = {0};

DMAMUX_0.CHCFG[4].B.TRIG = 0;

DMAMUX_0.CHCFG[4].B.SOURCE = 0x12;

DMAMUX_0.CHCFG[4].B.ENBL = 1;

DMA_0.CR.B.CX = 0; //normal operate mode

DMA_0.CR.B.ECX = 0;

DMA_0.CR.B.GRP1PRI = 1; //Fixed priority arbitration

DMA_0.CR.B.GRP0PRI = 0;

DMA_0.CR.B.EMLM = 1; //enable minor loop mapping and disable offset

DMA_0.CR.B.CLM = 0;

DMA_0.CR.B.HALT = 0;

DMA_0.CR.B.HOE = 0;

DMA_0.CR.B.ERGA = 0;

DMA_0.CR.B.ERCA = 0;

DMA_0.CR.B.EDBG = 0;

DMA_0.DCHPRI[4].R = 0x04; /* Grp 0 chan 04, no suspension, no premption */

DMA_0.TCD[4].SADDR.R = 0xFBE0011C; //ADC0_CH7_CH8_CDR_ADD

DMA_0.TCD[4].ATTR.B.SMOD = 0;

DMA_0.TCD[4].ATTR.B.SSIZE = 2; //uint32

DMA_0.TCD[4].SOFF.R = 4;

DMA_0.TCD[4].SLAST.R = 0;

DMA_0.TCD[4].DADDR.R = (uint32_t) adc0ChannelData;

DMA_0.TCD[4].ATTR.B.DMOD = 0;

DMA_0.TCD[4].ATTR.B.DSIZE = 2;

DMA_0.TCD[4].DOFF.R = 4;

DMA_0.TCD[4].DLASTSGA.R = -256; //只有在major loop 完成以后才执行这个步骤

DMA_0.TCD[4].NBYTES.MLOFFNO.B.SMLOE = 0; //minor loop enable and link-to-link disable

DMA_0.TCD[4].NBYTES.MLOFFNO.B.DMLOE = 0; //minor loop offset is applied to the SADDR

DMA_0.TCD[4].NBYTES.MLOFFNO.B.NBYTES = 4; //minor loop cnt

DMA_0.TCD[4].BITER.ELINKNO.B.ELINK = 0;

DMA_0.TCD[4].BITER.ELINKNO.B.BITER = 64;

DMA_0.TCD[4].CITER.ELINKNO.B.ELINK = 0;

DMA_0.TCD[4].CITER.ELINKNO.B.CITER = 64;

DMA_0.TCD[4].CSR.B.BWC = 0;

DMA_0.TCD[4].CSR.B.MAJORLINKCH = 0;

DMA_0.TCD[4].CSR.B.ACTIVE = 0;

DMA_0.TCD[4].CSR.B.DONE = 0;

DMA_0.TCD[4].CSR.B.MAJORELINK = 0;

DMA_0.TCD[4].CSR.B.ESG = 0;

DMA_0.TCD[4].CSR.B.INTHALF = 0;

DMA_0.TCD[4].CSR.B.INTMAJOR = 1;

DMA_0.TCD[4].CSR.B.START = 0;

DMA_0.ERQ.B.ERQ4 = 1;

I using multiple request to transfer data, I want to make adc0channeldata buffer storing adc0-ch7 and adc0-ch8 data. But i can't make sources address return to initial value when a minor loop completion.How should i do .

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm sorry that i misconfigure MSCR reg,it lead to waveform it noncorrection