- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX6 LVDS -24 bit mapping

iMX6 LVDS -24 bit mapping

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMX6 LVDS -24 bit mapping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

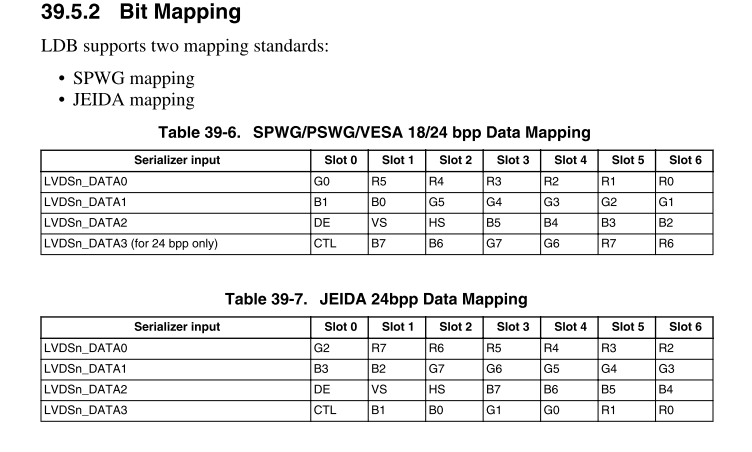

I am not clear about the 24 bit SPWG/PSWG/VESA data mapping given in imx6 technical reference manual section 39.5.2. In below table 39.6, R6,G6,B6 represents LSB color bit or 6th color bits ? ( when BIT_MAPPING_CH0 = 0 ,SPWG and DATA_WIDTH_CH0=1, 24 bit)

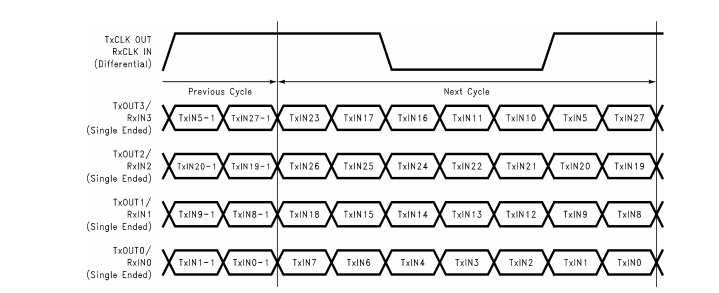

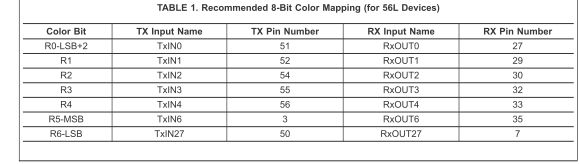

I am trying to interface 2 different 24 bit parallel RGB display with imx6 using LVDS0 port with Ti's deserilizer chip, DS90CF384A. In the below figure (table 1) R6 is LSB , R7 is LSB +1 , R0 is LSB+2 ,... and R5 is MSB and it is similar for Green and Blue data.

By comparing deserializer chip mapping and imx6 bit mapping, the data coming out of imx6 at LVDSn_DATA3 lane ( B6 B7 G6 G7 R6 R7 ) should be LSB in 24 bit map. is this correct?

If i considered the data coming out of imx6 at LVDSn_DATA3 lane (B6 B7 G6 G7 R6 R7 ) as MSB bits, one display is working properly and another 24 bit display doesn't work in this mapping ( corrupted colors)

if I considered those data as LSB as per deserilizer chip both displays images are not proper. can anyone confirm iMX6 side data mapping properly for 18 bit mode and 24 bit mode? Particularly for LVDSn_DATA3 lane.

Thanks,.

Tamilarasn

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please refer to attached OpenLDI Specification document and compare the data mapping, given on the Figure 5-3 of this document, with the i.MX6 24-bit LVDS data mapping, given in the Table 39-6 of the i.MX6Dual/Quad Reference Manual document. As it can be seen, the answer is: yes, the LVDS data mapping is denoted correctly for the i.MX6 processors, and B6, B7, G6, G7, R6, R7 mean the MSB color bits.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------