- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- ADC16 Asynch clock Information

ADC16 Asynch clock Information

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC16 Asynch clock Information

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using MKL17Z32VFM4, ADC in 16bits diff mode, triggered with TPM at constant frequency for several samples (about 10). So first sample have the same given time with TPM than next ones. I want to optimize speed to decrease consumption, and also want low noise.

For noise, I am willing to use the asynk clock, but I cant find the necessary information ...

How do this clock work ? I see how to enable it, I see it connection on the Block diagram, but without any input for clk ? what frequency is it?

Is there a reel difference for noise compared to normal clock ? as on "Typical ENOB vs. ADC_CLK for 16-bit differential mode" it the graph goes up to 12Mhz, and at the same time for asynk clock, it is specified 9.5Mhz max.

In the Manuel for ADACKEN, it is written : "Also, latency of initiating a single or first-continuous conversion with the asynchronous clock selected is reduced because the ADACK clock is already operational."

What latency will have the first samples with/without ADACKEN ? Especially regarding sample.

Thanks,

Matt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Matt,

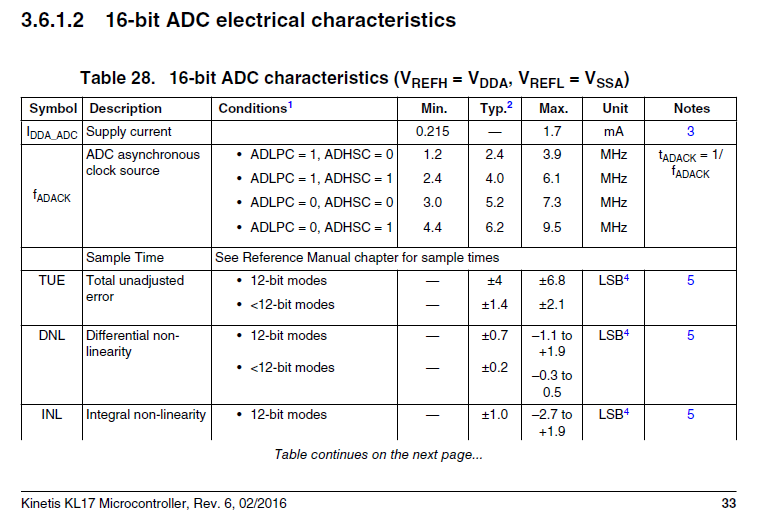

The ADACK clock is an internal clock for only ADC module, I attach the clock frequency specs from the data sheet of KL17.

From the table, you know it varies from 1.0MHz to 9.5MHz based different register setting. In the case ADLPC=0 ADHSC=1, the typical frequency is 6.2MHz. Based on the graph ADC 16-bit Differential ENOB vs ADC Clock, I think 6.2MHz clock is okay to get high ENOB.

Regarding how to use the ADACK clock, before you use it, set the ADCx_CFG2[ADACKEN]=1, set the ADCx_CFG1[ADICLK] =11, then you can use the ADACK as ADC clock.

Regarding the remark "Also, latency of initiating a single or first-continuous conversion with the asynchronous clock selected is reduced because the ADACK clock is already operational.", this is my opinion, if the you configure:

the ADCx_CFG2[ADACKEN]=0, //the ADACK is disabled

the ADCx_CFG1[ADICLK] =11

you can still start the ADC to convert, the ADC will automatically enable the ADACK when you start ADC conversion, after conversion is complete, the ADACK is disabled automatically, in this way, the power consumption can decrease, but the latency will be introduced in the case.

If you configure:

the ADCx_CFG2[ADACKEN]=1, //the ADACK is enabled

the ADCx_CFG1[ADICLK] =11

The ADACK is enabled always, there is not any latency.

Hope it can help you

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the response, it is clear for Asynchronous clk (I misread data-sheet). A remark is I find it is a very wide min max ! (min 4.4Mhz and max 9.5Mhz)

I tested, and regarding my tests, Asynchronous clk do not give less noise for me ! But I see the advantage of ADACK to have the less coupled noise (for big oversampling/averages) => for my application 12 Mhz is good !

Meanwhile doing my tests on ADACK, regarding ADACKEN, a strange thing was that the minimum time I managed to have between successive single samples, are exactly the same with and without ADACKEN ??

Regards,

Matt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Matt,

I think the conversion time is different with or without ADACKEN, when the ADACKEN is cleared, after you launch the ADC to convert, the Asynchronous clk starts to work, the clock stable time is required.

I recommend you set the ADACKEN bit so that the Asynchronous clk is always enabled.

Hope it can help you

BR

Xiangjun Rong