- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- linux pcie dts

linux pcie dts

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

linux pcie dts

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Now I have a problem about pcie dts. In ls1021a.dtsi, have a pcie description:

pcie@3400000 {

compatible = "fsl,ls1021a-pcie", "snps,dw-pcie";

reg = <0x00 0x03400000 0x0 0x00010000 /* controller registers */

0x40 0x00000000 0x0 0x00002000>; /* configuration space */

reg-names = "regs", "config";

interrupts = <GIC_SPI 181 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 183 IRQ_TYPE_LEVEL_HIGH>; /* aer interrupt */

interrupt-names = "pme", "aer";

fsl,pcie-scfg = <&scfg 0>;

#address-cells = <3>;

#size-cells = <2>;

device_type = "pci";

num-lanes = <4>;

bus-range = <0x0 0xff>;

ranges = <0x81000000 0x0 0x00000000 0x40 0x00010000 0x0 0x00010000 /* downstream I/O */

0x82000000 0x0 0x40000000 0x40 0x40000000 0x0 0x40000000>; /* non-prefetchable memory */

msi-parent = <&msi>;

#interrupt-cells = <1>;

interrupt-map-mask = <0 0 0 7>;

interrupt-map = <0000 0 0 1 &gic GIC_SPI 91 IRQ_TYPE_LEVEL_HIGH>,

<0000 0 0 2 &gic GIC_SPI 188 IRQ_TYPE_LEVEL_HIGH>,

<0000 0 0 3 &gic GIC_SPI 190 IRQ_TYPE_LEVEL_HIGH>,

<0000 0 0 4 &gic GIC_SPI 192 IRQ_TYPE_LEVEL_HIGH>;

};

pcie@3500000 {

compatible = "fsl,ls1021a-pcie", "snps,dw-pcie";

reg = <0x00 0x03500000 0x0 0x00010000 /* controller registers */

0x48 0x00000000 0x0 0x00002000>; /* configuration space */

reg-names = "regs", "config";

interrupts = <GIC_SPI 182 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 184 IRQ_TYPE_LEVEL_HIGH>; /* aer interrupt */

interrupt-names = "pme", "aer";

fsl,pcie-scfg = <&scfg 1>;

#address-cells = <3>;

#size-cells = <2>;

device_type = "pci";

num-lanes = <4>;

bus-range = <0x0 0xff>;

ranges = <0x81000000 0x0 0x00000000 0x48 0x00010000 0x0 0x00010000 /* downstream I/O */

0x82000000 0x0 0x40000000 0x48 0x40000000 0x0 0x40000000>; /* non-prefetchable memory */

msi-parent = <&msi>;

#interrupt-cells = <1>;

interrupt-map-mask = <0 0 0 7>;

interrupt-map = <0000 0 0 1 &gic GIC_SPI 92 IRQ_TYPE_LEVEL_HIGH>,

<0000 0 0 2 &gic GIC_SPI 189 IRQ_TYPE_LEVEL_HIGH>,

<0000 0 0 3 &gic GIC_SPI 191 IRQ_TYPE_LEVEL_HIGH>,

<0000 0 0 4 &gic GIC_SPI 193 IRQ_TYPE_LEVEL_HIGH>;

};

In reg property, why does configuration space set 0x40 or 0x48? what's mean of the address of 0x40 or 0x48?

Please help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have a great day,

If you look from the root of the tree you can see that parent of these nodes has

#address-cells = <2>;

#size-cells = <2>;

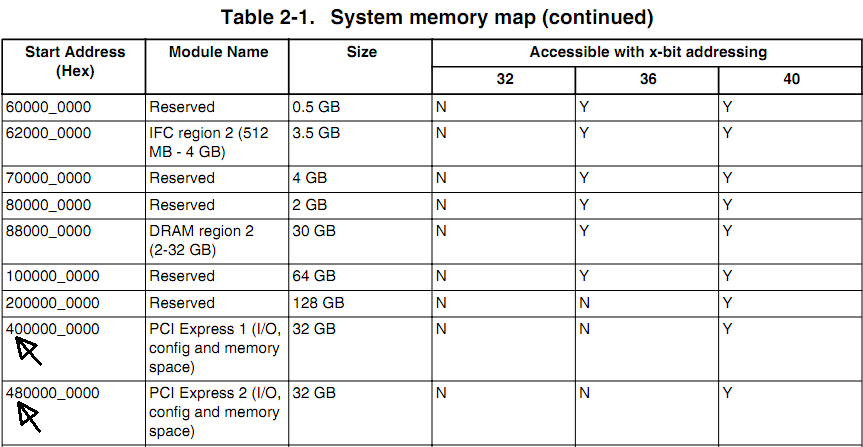

So in the <reg> we need 4 32-bit values for single pair address : size on this bus. So each <reg> specifies that PCIe@340000 node occupies <0x0 0x00002000> = 0x2000 bytes at address <0x40 0x00000000> = 0x4000000000 while the second PCIe occupies 0x2000 bytes at address 0x4800000000. The same PCIe@340000 <range> refers to the addresses <0x40 0x40000000> = 0x4040000000 and 0x4000010000 , while PCIe@350000 <range> refers to the addresses 0x4840000000 and 0x4800010000

It is in accordance to the LS1021A memory map. The LS1021A reference manual table 2-1 shows

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Now I understand these. Thank you very much!