- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5746R eTPU requirement for IGF

MPC5746R eTPU requirement for IGF

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5746R eTPU requirement for IGF

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems that eTPU2 inputs require that the Input Glitch Filter (IGF) is configured before they will work.

Is this mentioned in the MPC5746RRM ? I don't seem able to find it. Only by chance did I stumble upon this critical information in the 5634M - 5746R migration guide document.

It would be handy to have a code snippet showing the multiple configurations required to get an eTPU pin to actually be an input.

e.g.

MPC5634M code was simple:

SIU.PCR[114].R = 0x0503; /* Configure pad for primary eTPU_A[0] input and PU */

MPC5746R appears to require lots more if I'm understanding it correctly:

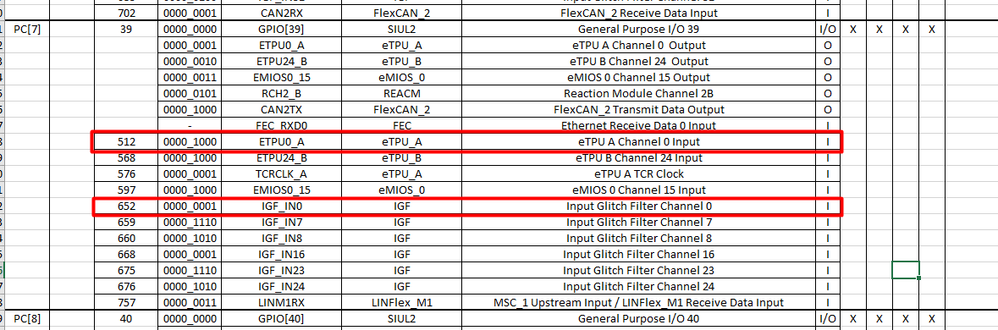

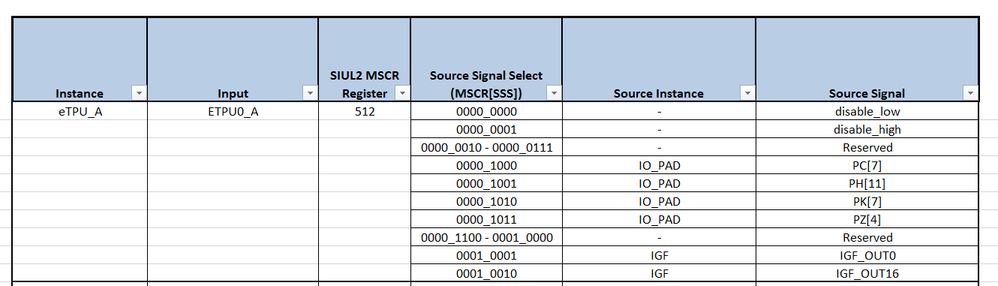

SIUL2.MSCR0_255[39].R = 0x003d0000; /* Configure PC7 pad for primary eTPU_A[0] input and PU */

SIUL2.MSCR512_995[576-512].R = 1; /* set as eTPU_A TCRCLK_A input */

SIUL2.MSCR512_995[652-512].R = 1; /* PC7 -> IGF0 -> eTPU_A0 */

/* Configure input glitch filter for crank and cam inputs as bypass */

IGF.MCR.B.MDIS = 0;

IGF.MCR.B.FGEN = 0;

IGF.MCR.R = 0; /* set rising and falling to bypass */

IGF.MCR.B.FGEN = 1; /* enable filter */

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How about when using it as a TRCLK input?

I will retest my code later in the week, but until I added the IGF configuration, nothing seemed to be happening.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well.... I tested this with my IGF setup code removed and it still works ?!

So, looks like I raised a false alarm. Sorry about that. I'm not sure why I couldn't get it working initially though.

However, please explain what this means in AN4658

"After system reset, the IGF modules are in Configuration mode by default. This mode disables IGF output and prevents the signals from the pins from reaching the eMIOS and eTPU modules"

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

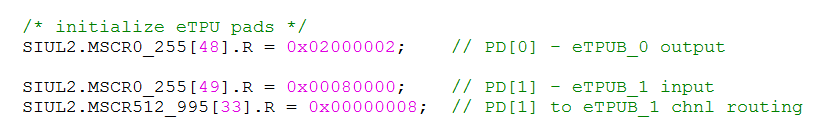

I was also testing it with MPC5777C device where really it is needed to configure IGF module, but MPC5777C used different pads, it works slightly different way:

Example MPC5777C-eTPU_GPIO_test GHS714

Back to MPC5746R:

Author of AN4658 no longer works in the company so I cannot check it with him. It is possible some preliminary version had it implemented this way. Also Figure 45-1 in RM seems to me unclear. I will ask for changing it to see direct path between pad and IOMUX.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I know Input Glitch Filter is new option available on MPC57xx devices, it is not part of eTPU2 (already use with some MPC56xx). It is not necessary to use it, you may use backward compatible option and route these signal directly to eTPU module.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In my testing that did not work.

AN4658 says "After system reset, the IGF modules are in Configuration mode by default. This mode disables IGF output and prevents the signals from the pins from reaching the eMIOS and eTPU modules"

MPC5746RRM doesn't appear to mention this.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have just tested it and it works on my side as expected. Having connected eTPUB0 (general purpose output) and eTBUB1 (general purpose input) together, I am able to read inputs values without setting of Input Glitch Filter properly.