- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Debug T2080RDB vxworks bootrom with codewarrior tap and tools

Debug T2080RDB vxworks bootrom with codewarrior tap and tools

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Debug T2080RDB vxworks bootrom with codewarrior tap and tools

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

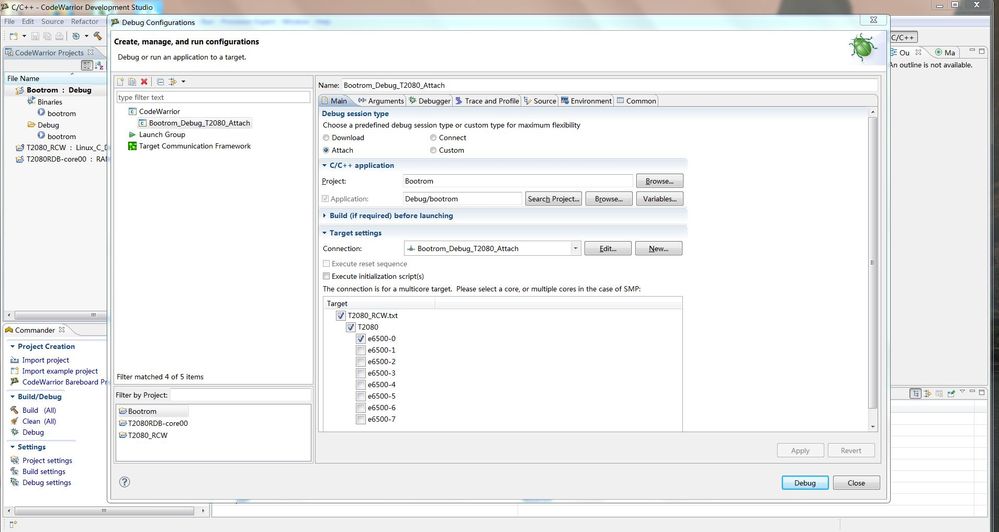

How to Debug T2080RDB vxworks bootrom with codewarrior tap and tools?

I want to debug the bootrom image by step into the bootrom code in flash memory location 0xfff00000-0xffffffff

Attached the memory map in vxworks6.x for T2080QDS &RDB

\sh Memory Maps

The default hardware memory map of the XT2080QDS BSP is as follows:

\ts

Start | Size | End | Access to

----------------------------------------------------

0x0000_0000 | 2GB | 0x7FFF_FFFF | DDR3 SDRAM

0x7F40_0000 | 8MB | 0x7FBF_FFFF | 8MB reserved memory for QMAN hardware

0x7FC0_0000 | 4MB | 0x7FFF_FFFF | 4MB reserved memory for BMAN hardware

0x8000_0000 | 64MB | 0x83FF_FFFF | PCIe 1 Prefetchable Memory

0x8400_0000 | 64MB | 0x87FF_FFFF | PCIe 1 Non-Prefetchable Memory

0x8800_0000 | 64MB | 0x8BFF_FFFF | PCIe 1 IO

0x8C00_0000 | 64MB | 0x8FFF_FFFF | PCIe 1 IO32

0xA000_0000 | 64MB | 0xA3FF_FFFF | PCIe 2 Prefetchable Memory

0xA400_0000 | 64MB | 0xA7FF_FFFF | PCIe 2 Non-Prefetchable Memory

0xA800_0000 | 64MB | 0xABFF_FFFF | PCIe 2 IO

0xAC00_0000 | 64MB | 0xAFFF_FFFF | PCIe 2 IO32

0xC000_0000 | 64MB | 0xC3FF_FFFF | PCIe 3 Prefetchable Memory

0xC400_0000 | 64MB | 0xC7FF_FFFF | PCIe 3 Non-Prefetchable Memory

0xC800_0000 | 64MB | 0xCBFF_FFFF | PCIe 3 IO

0xCC00_0000 | 64MB | 0xCFFF_FFFF | PCIe 3 IO32

0xD000_0000 | 64MB | 0xD3FF_FFFF | PCIe 4 Prefetchable Memory

0xD400_0000 | 64MB | 0xD7FF_FFFF | PCIe 4 Non-Prefetchable Memory

0xD800_0000 | 64MB | 0xDBFF_FFFF | PCIe 4 IO

0xDC00_0000 | 64MB | 0xDFFF_FFFF | PCIe 4 IO32

0xEFDF_0000 | 4KB | 0xEFDF_0FFF | QIXIS

0xF400_0000 | 32MB | 0xF5FF_FFFF | BMAN

0xF600_0000 | 32MB | 0xF7FF_FFFF | QMAN

0xFD00_0000 | 4MB | 0xFD3F_FFFF | DCSR

0xFE00_0000 | 16MB | 0xFEFF_FFFF | CCSBAR

0xFF00_0000 | 16MB | 0xFFFF_FFFF | NOR FLASH

I modify the the T2080RDB-PCIe_init_sram.tcl

with following changes:

##################################################################################

# Local Access Windows Setup

## LAW1 to IFC- QIXIS

# LAWBARH

mem [CCSR_ADDR 0x000C10] = 0x00000000

# LAWBARL

mem [CCSR_ADDR 0x000C14] = 0xEFDF0000

# LAWAR

mem [CCSR_ADDR 0x000C18] = 0x81F0000B

## LAW2 to IFC - NOR

# LAWBARH

mem [CCSR_ADDR 0x000C20] = 0x00000000

# LAWBARL

mem [CCSR_ADDR 0x000C24] = 0xFF000000

# LAWAR

mem [CCSR_ADDR 0x000C28] = 0x81f0001a

# clear the other CSPRs to be able to read from QIXIS before the final configuration

mem [CCSR_ADDR [expr 0x124010 + 0 * 0x0C]] = 0x00000000

mem [CCSR_ADDR [expr 0x124010 + 1 * 0x0C]] = 0x00000000

mem [CCSR_ADDR [expr 0x124010 + 2 * 0x0C]] = 0x00000000

# QIXIS, addr 0xFFDF0000, 4k size, 8-bit, GPCM, Valid

# CSPR_EXT

mem [CCSR_ADDR [expr 0x12400C + $QIXIS_CS * 0x0C]] = 0x00000000

# CSPR

mem [CCSR_ADDR [expr 0x124010 + $QIXIS_CS * 0x0C]] = 0xEFDF0085

# AMASK

mem [CCSR_ADDR [expr 0x1240A0 + $QIXIS_CS * 0x0C]] = 0x00000000

# CSOR

mem [CCSR_ADDR [expr 0x124130 + $QIXIS_CS * 0x0C]] = 0x00000000

# IFC_FTIM0

mem [CCSR_ADDR [expr 0x1241C0 + $QIXIS_CS * 0x30]] = 0xE00E000E

# IFC_FTIM1

mem [CCSR_ADDR [expr 0x1241C4 + $QIXIS_CS * 0x30]] = 0xFF003F00

# IFC_FTIM2

mem [CCSR_ADDR [expr 0x1241C8 + $QIXIS_CS * 0x30]] = 0x0E00001F

# IFC_FTIM3

mem [CCSR_ADDR [expr 0x1241CC + $QIXIS_CS * 0x30]] = 0x00000000

# NOR Flash, addr 0xFF000000, 16MB size, 16-bit NOR

# CSPR_EXT

mem [CCSR_ADDR [expr 0x12400C + $NOR_CS * 0x0C]] = 0x00000000

# CSPR

mem [CCSR_ADDR [expr 0x124010 + $NOR_CS * 0x0C]] = 0xFF000101

# AMASK

mem [CCSR_ADDR [expr 0x1240A0 + $NOR_CS * 0x0C]] = 0xFF000000

# CSOR

mem [CCSR_ADDR [expr 0x124130 + $NOR_CS * 0x0C]] = 0x0000000c

# IFC_FTIM0

mem [CCSR_ADDR [expr 0x1241C0 + $NOR_CS * 0x30]] = 0x40050005

# IFC_FTIM1

mem [CCSR_ADDR [expr 0x1241C4 + $NOR_CS * 0x30]] = 0x35001A13

# IFC_FTIM2

mem [CCSR_ADDR [expr 0x1241C8 + $NOR_CS * 0x30]] = 0x0410381C

# IFC_FTIM3

mem [CCSR_ADDR [expr 0x1241CC + $NOR_CS * 0x30]] = 0x00000000

##################################################################################

# MMU initialization

#

set CCSR_EPN 000000[string range [CCSR_ADDR 1] 4 14]

set CCSR_RPN [string range [CCSR_ADDR 0] 4 14]

# define 16MB TLB entry 1 : 0xFE000000 - 0xFEFFFFFF for CCSR cache inhibited, guarded

reg ${CAM_GROUP}L2MMU_CAM1 = 0x7000000A1C080000000000${CCSR_RPN}${CCSR_EPN}

# define 256k TLB entry 2 : 0x00000000 - 0x0003FFFF for SRAM cache-inhibited

reg ${CAM_GROUP}L2MMU_CAM2 = 0x480000081C08000000000000000000000000000000000001

# define 256k TLB entry 3 : 0x00040000 - 0x0007FFFF for SRAM cache-inhibited

reg ${CAM_GROUP}L2MMU_CAM3 = 0x480000081C08000000000000000400000000000000040001

# define 4k TLB entry 4 : 0xFFDF0000 - 0xFFDF0FFF for QIXIS cache-inhibited, guarded

reg ${CAM_GROUP}L2MMU_CAM4 = 0x1000000A1C08000000000000EFDF000000000000EFDF0001

# define 16M TLB entry 5 : 0xFF000000 - 0xFFFFFFFF for NOR cache-inhibited, guarded

reg ${CAM_GROUP}L2MMU_CAM5 = 0x7000000A1C08000000000000FF00000000000000FF000001

T2080RDB-PCIe.mem

translate v:0x0000000000000000 i:0x0000000000 0x80000000

translate v:0x00000000C0000000 i:0x00C0000000 0x20000000

translate v:0x00000000FF000000 i:0x00FF000000 0x01000000

translate v:0x00000000FE000000 i:0x00FE000000 0x01000000

//translate v:0x00000000FF800000 i:0x00FF800000 0x00100000

translate v:0x00000000EFDF0000 i:0x00EFDF0000 0x00001000

translate v:0x00000000FFFFF000 i:0x00FFFFF000 0x00001000

AutoEnableTranslations true

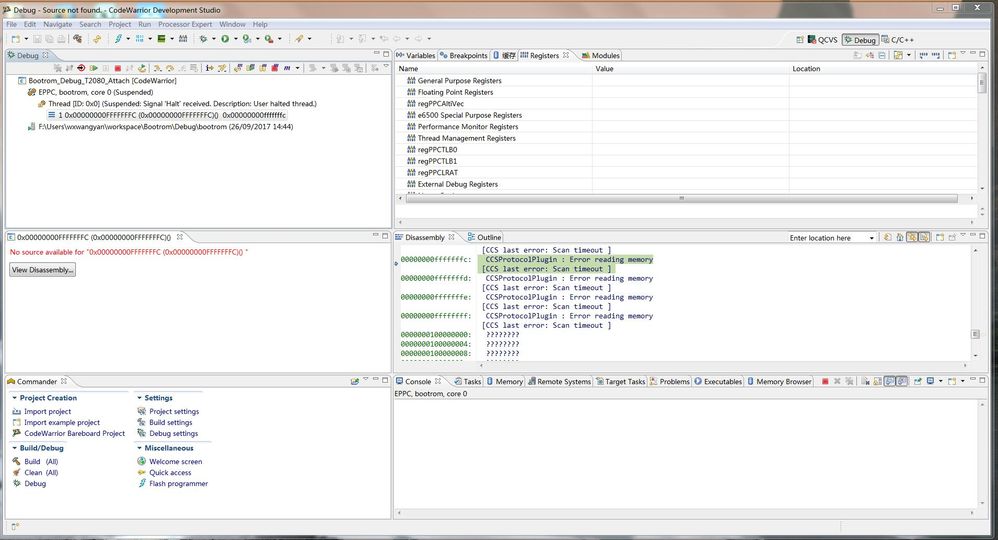

But when codewarrior initialed the board, the tool can't access the flash memory range 0xFF000000..

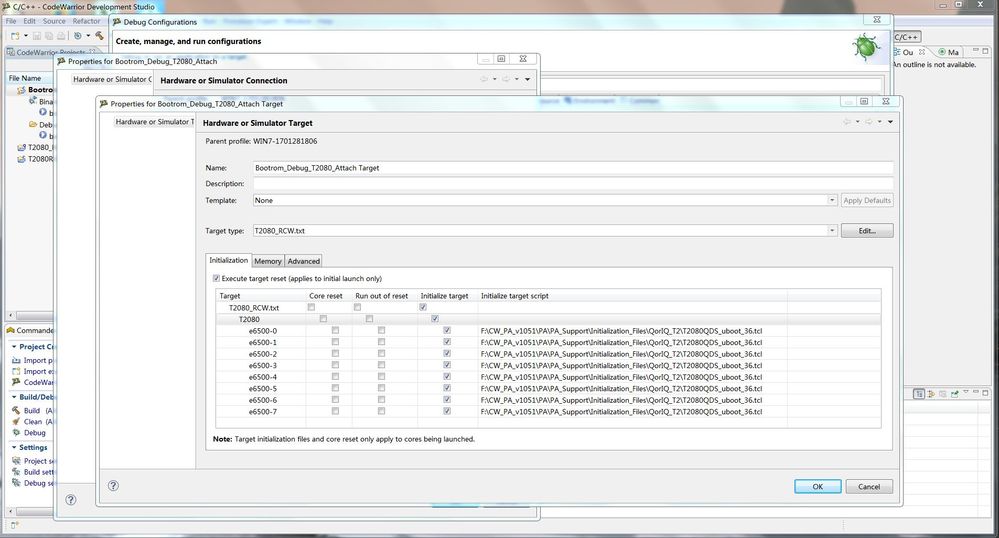

I also use the T2080RDB_uboot_36.tcl and T2080RDB-PCIe_uboot_36_NOR_stage1.mem to initial the board,

after codewarriot attached the board, it will failed to access 0xFFFFFFFC.

T2080QDS_uboot_36.tcl

proc envsetup {} {

# Environment Setup

radix x

config hexprefix 0x

config MemIdentifier v

config MemWidth 32

config MemAccess 32

config MemSwap off

}

#-------------------------------------------------------------------------------

# Main

#-------------------------------------------------------------------------------

envsetup

#######################################################################

# debugger settings

variable GPR_GROUP "General Purpose Registers/"

# prevent stack unwinding at entry_point/reset when stack pointer is not initialized

reg ${GPR_GROUP}SP = 0x000000000000000F

T2080RDB-PCIe_uboot_36_NOR_stage1.mem

reservedchar 0xBA

reserved v:0x00000000 v:0xFFFFEFFF

reserved p:0x00000000 p:0xFFFFEFFF

reserved i:0x00000000 i:0xFFFFEFFF

reserved v:0x100000000 v:0xFFFFFFFFFFFFFFFF

reserved p:0x100000000 p:0xFFFFFFFFF

reserved i:0x100000000 i:0xFFFFFFFFF

translate v:0x00000000FFFFF000 i:0x00FFFFF000 0x00001000

AutoEnableTranslations true

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

NXP offers CodeWarrior 10.5.1 for Power Architecture:

https://nxp.flexnetoperations.com/control/frse/download?element=7360217

Documentation for this CodeWarrior contains description for debugging u-boot or Linux kernel. Perhaps similar possibility can be used for your task. See the Targeting_PA_Processors.pdf file. Find the "Debugging U-Boot using NOR, NAND, SPI, and SD Card/MMC Flash Devices" and "Debugging the Linux Kernel" in this document.

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

add the initial script file

failed to access 0xFFFFFFFC,

I use the T2080RDB_uboot_36.tcl and T2080RDB-PCIe_uboot_36_NOR_stage1.mem to initial the board,

after codewarriot attached the board, it will failed to access 0xFFFFFFFC.

T2080QDS_uboot_36.tcl

proc envsetup {} {

# Environment Setup

radix x

config hexprefix 0x

config MemIdentifier v

config MemWidth 32

config MemAccess 32

config MemSwap off

}

#-------------------------------------------------------------------------------

# Main

#-------------------------------------------------------------------------------

envsetup

#######################################################################

# debugger settings

variable GPR_GROUP "General Purpose Registers/"

# prevent stack unwinding at entry_point/reset when stack pointer is not initialized

reg ${GPR_GROUP}SP = 0x000000000000000F

T2080RDB-PCIe_uboot_36_NOR_stage1.mem

reservedchar 0xBA

reserved v:0x00000000 v:0xFFFFEFFF

reserved p:0x00000000 p:0xFFFFEFFF

reserved i:0x00000000 i:0xFFFFEFFF

reserved v:0x100000000 v:0xFFFFFFFFFFFFFFFF

reserved p:0x100000000 p:0xFFFFFFFFF

reserved i:0x100000000 i:0xFFFFFFFFF

translate v:0x00000000FFFFF000 i:0x00FFFFF000 0x00001000

AutoEnableTranslations true

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Because vxworks bootrom for Qoriq flash address locate at 0xFF000000 - 0xFFFFFFFF,

and Uboot's flash address is at 0xEFFF0000- 0xEFFFFFFF.

How to setup the initial script file to debug vxworks bootrom in codewarrior?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

add the initial script file