- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- [KEAZN64] Watchdog ISR is not working

[KEAZN64] Watchdog ISR is not working

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[KEAZN64] Watchdog ISR is not working

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am working on controller KEAZN64 (Cortex M0).

I am trying to implement a staff inside the ISR of the watchdog interrupt before reset.

However, when i write this sample of code;

_INTERRUPT void WDG_IRQHandler (void)

{

PORTA_SET_PIN(_BIT1);

}

and do a breakpoint at line including "PORTA" or wait for PORTA to detect the edge '1'.

Both ways show that ISR is not called after watchdog overflows.

Could someone help me to implement the ISR in a good manner please ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mohammed,

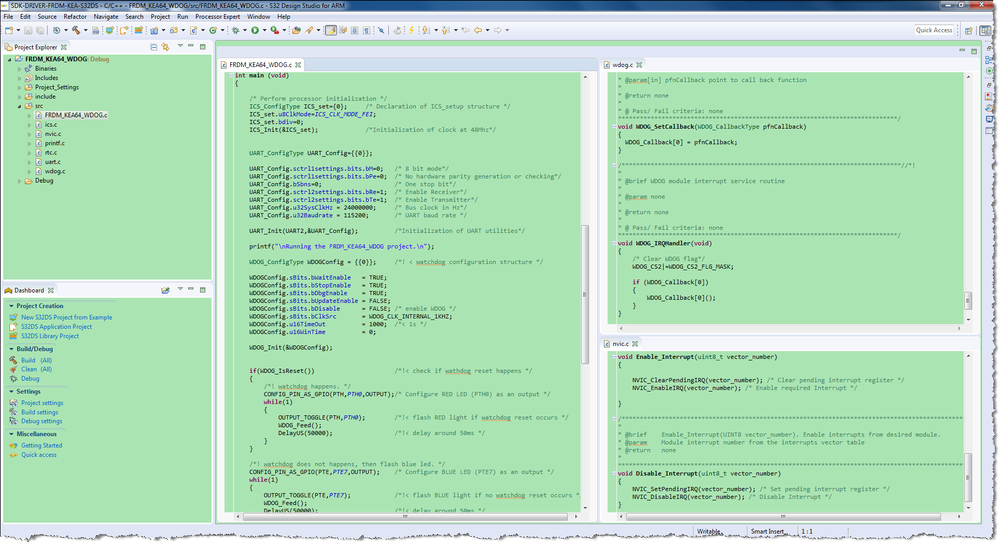

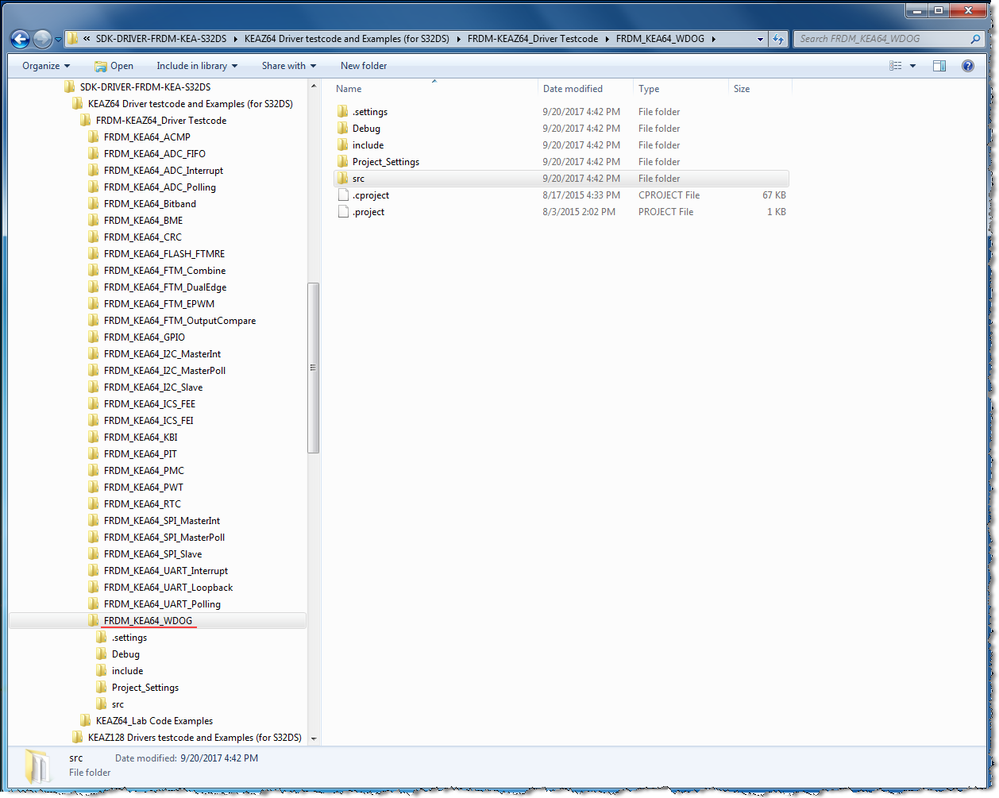

Please download the 'SDK Software Drivers for KEAZ128_KEAZ64 using S32DS' and refer the FRDM_KEA64_WDOG example. You can open this example by using S32DS: S32 Design Studio IDE.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Mohammed

I use this code:

// Watchdog initialisation

UNLOCK_WDOG();

WDOG_CS2 = (WDOG_CS2_CLK_1kHz | WDOG_CS2_FLG);

WDOG_TOVAL = BIG_SHORT_WORD(2000);

WDOG_WIN = 0;

WDOG_CS1 = (WDOG_CS1_INT | WDOG_CS1_EN); // enable watchdog with 2s timeout (no update capability and interrupt 128 bus clocks before the HW reset takes place)

//Enter watchdog handler and enable source in NVIC

fnEnterInterrupt(irq_WDOG_ID, 0, wdog_irq); // test WDOG interrupt (highest priority)

// Watchdog handler

static void wdog_irq(void)

{

WDOG_CS2 |= WDOG_CS2_FLG; // clear interrupt flag

*BOOT_MAIL_BOX = 0x9876; // set a pattern to the boot mailbox to show that the watchdog interrupt took place

}

Note that it is usually not possible to use a debugger to detect the ISR firing since the HW reset takes place unconditionally 128 bus cycles later, which causes the debugger to immediately move to the reset vector instead.

Regards

Mark

http://www.utasker.com/kinetis/FRDM-KEAZ64Q64.html

http://www.utasker.com/kinetis/TRK-KEA64.html