- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Identification and Security

- :

- NFC

- :

- Allowed I2C rise- and fall-times

Allowed I2C rise- and fall-times

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Allowed I2C rise- and fall-times

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

i have a question about the allowed fall-times of I2C-signals of the NFC-driver NT3H2111W0FHK.

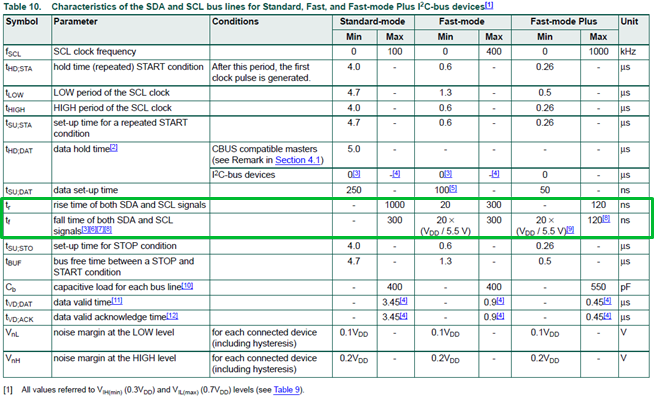

In the linked document "I2C-bus specification and user manual" UM10204 (Rev. 6 - 4 April 2014) one can find different allowed rise- and fall-times for the signals depending on the used mode (which makes sense so far):

But why are limits for minimum fall-times only defined in some cases but not in other?

Currently the standard-mode allows faster fall times than fast-mode or fast-mode plus. The minimum limits for rise-times are even stranger: standard-mode and fast-mode plus support faster rise-times than fast mode.

In our application (fast-mode) the measured fall time is only about 3-5ns - but the minimum allowed fall time according the spec would be 10ns. - Could this cause any issues?

We could change the communication speed and would be fine with the limits but this would waste valuable time if this measure is not absolutely necessary.

Thanks,

Roland

P.S. footnote [1] seems to be incorrect: VIHmin is lower than VILmax.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Interesting question on the fall time requirement. It looks like the fall time requirement is as pointed by Kan-Li. However the question from Roland is how to meet the requirement when existing measure does not.

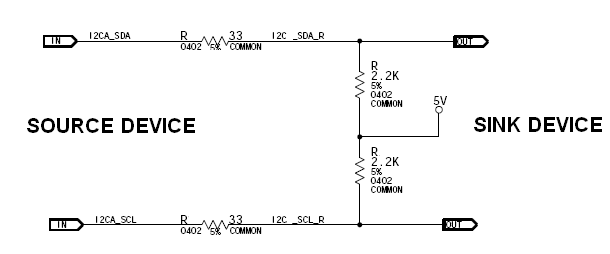

The simplest approach is to add a series resistor between the output driver of the I2C and the I2C connection. Based on the fall time and the Vih and ViL, we can estimate the fall time

CR = Tau ~= Tf (Note fall time 90->10% is 1.4CR, so 70% to 30% is about 1CR by estimation without going into details)

R = Tf/C R = series resistor, C = bus capacitance

Assuming C = 100pf

Fall time requirement 10ns (from your requirment)

Tf - 10ns (assuming another 10ns from your requirement meaning 10 + 3ns)

R = 10E-9/100E-12 = 100 ohms (replace the 33 ohm below with 100 ohms)

Also addition bus capacitance which Roland did will not help much because when the SCL or SDA is turned on the capacitance is shorted with little resistance during fall time period. That is the reason the increase in fall time is so insignificant.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

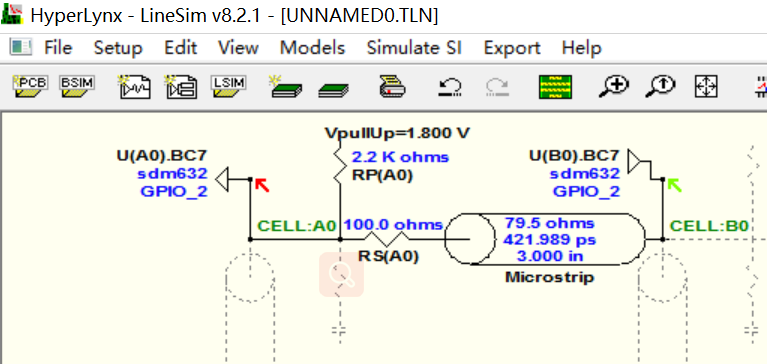

I have been encountering I2C fall time problem. According to UM10204.pdf, I add an series resistor about 100ohm like your picture above, but when I use hyperlynx simulate fall time, it has almost been changed. My understanding is that rise time is related with pull-up resistor and capacitance load ,Cb in UM10204.pdf. I don't know why fall time can be calculated by this equation, and here R is the series resistor value. Hope your reply. My number is 18611760398.Thanks a lot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Roland,

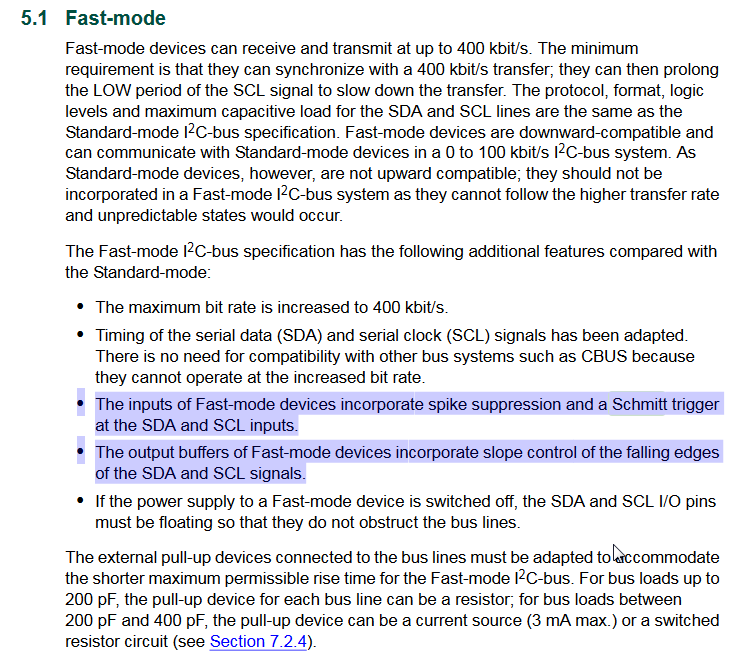

On page 36, the UM10204 says as below:

I think that is the reason why there is minimum falling time defined for fast mode/fast mode plus, so please don't make it out of spec.

Hope that makes sense,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------