- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- AUD_RXC and AUD_RXFS UART3 RX/TX conflict on 6sl

AUD_RXC and AUD_RXFS UART3 RX/TX conflict on 6sl

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

AUD_RXC and AUD_RXFS UART3 RX/TX conflict on 6sl

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm using a custom i.mx6sl board running Linux 4.1.15 and trying to get bluetooth working. I'm using the following DTS settings:

MX6SL_PAD_AUD_RXFS__UART3_RX_DATA 0x1b0b1

MX6SL_PAD_AUD_RXC__UART3_TX_DATA 0x1b0b1

MX6SL_PAD_EPDC_BDR0__UART3_RTS_B 0x1b0b1

MX6SL_PAD_EPDC_BDR1__UART3_CTS_B 0x1b0b1

The problem I have is about configuring AUD_RXFS as UART3_RX and AUD_RXC as UART3_TX. The problem lies with IOMUXC_UART3_UART_RX_DATA_SELECT_INPUT. The datasheet says:

Route RX_DATA signal to pad when UART is in DCE mode. Route TX_DATA signal to pad when UART is

in DTE mode.

000 AUD_RXC_ALT2 — Selecting ALT2 mode of pad AUD_RXC for UART3_TX_DATA.

001 AUD_RXFS_ALT2 — Selecting ALT2 mode of pad AUD_RXFS for UART3_RX_DATA.

Does that mean I can't actually use AUD_RXFS as UART3_RX and at the same time have AUD_RXC as UART3_TX?

In testing, I'm seeing that I can't actually transmit anything on UART3 (ttymxc2).

root@imx6slevk:~# cat /proc/tty/driver/IMX-uart

serinfo:1.0 driver revision:

0: uart:IMX mmio:0x02020000 irq:21 tx:31181 rx:1126 RTS|DTR|DSR|CD

2: uart:IMX mmio:0x02034000 irq:23 tx:0 rx:0 DSR|CD

3: uart:IMX mmio:0x02038000 irq:24 tx:3 rx:0 DSR|CD

I checked that physically the pinmux has been configured correctly except for the confusion around IOMUXC_UART3_UART_RX_DATA_SELECT_INPUT

a) check rx pin

# check IOMUXC_SW_MUX_CTL_PAD_AUD_RXFS is set to 2 ALT2 UART3_RX_DATA.

/unit_tests/memtool -32 0x020E0058 1

# check (IOMUXC_UART3_UART_RX_DATA_SELECT_INPUT) is set to 1 AUD_RXFS_ALT2 — Selecting ALT2 mode of pad AUD_RXFS for UART3_RX_DATA

/unit_tests/memtool -32 0x20E080C 1

0x020E0058: 00000002

0x020E080C: 00000001

b) check tx pin

# check IOMUXC_SW_MUX_CTL_PAD_AUD_RXC is set to 2 UART3_TX_DATA.

/unit_tests/memtool -32 0x020E0050 1

0x020E0050: 00000002

But IOMUXC_UART3_UART_RX_DATA_SELECT_INPUT can't be set to 0 since it needs to be set to 1 so that RXFS is UART3_RX.

I think this means that I made a design mistake when selecting AUD_RXFS and AUD_RXC as the pads for UART3_RX and TX on this board and that means I won't be able to get this to work unless I find new pads that can carry UART3_RX and TX without conflict.

I would appreciate confirmation or advice/suggestions on this.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jaya Kumar,

It’s correct, there is a conflict in trying to use this configuration but you may use alternate pins for these functions . I would recommend using the Pins Tool for i.MX in order to review all muxing options of your design to make sure you do not run into similar issues with other muxing options.

I hope this helps!

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello gusarambula,

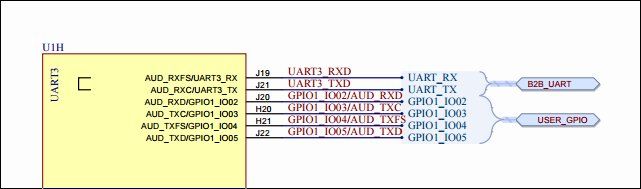

Thanks for your reply. Just to confirm, are you 100% sure there is a conflict in this configuration for UART3 using AUD_RXFS/RXC? The reason I ask is because I see the mx6sl Warp board reference design ( http://revotics.com/assets/warp/WaRP_Mainboard_r1.11_Schematics.PDF )used the same AUD_RXFS/RXC pins that I'm using for UART3 (pic attached). Did that board have a problem?

In addition, I also just tried setting it up with Pin Tools v3.0.2 and that doesn't give any error when I set up AUD_RXC and AUD_RXFS as UART3, it says the configuration is valid. It generates the following pin_mux.c

HW_IOMUXC_SW_MUX_CTL_PAD_AUD_RXC_WR(IOMUXC_BASE,

BF_IOMUXC_SW_MUX_CTL_PAD_AUD_RXC_MUX_MODE(BV_IOMUXC_SW_MUX_CTL_PAD_AUD_RXC_MUX_MODE_ALT2)); /* MUX Mode Select Field: Select signal UART3_TX_DATA.- Configure register IOMUXC_UART3_UART_RX_DATA_SELECT_INPUTSelect Input Register for mode ALT2. */

HW_IOMUXC_SW_MUX_CTL_PAD_AUD_RXFS_WR(IOMUXC_BASE,

BF_IOMUXC_SW_MUX_CTL_PAD_AUD_RXFS_MUX_MODE(BV_IOMUXC_SW_MUX_CTL_PAD_AUD_RXFS_MUX_MODE_ALT2)); /* MUX Mode Select Field: Select signal UART3_RX_DATA.- Configure register IOMUXC_UART3_UART_RX_DATA_SELECT_INPUTSelect Input Register for mode ALT2. */

HW_IOMUXC_UART3_UART_RX_DATA_SELECT_INPUT_WR(IOMUXC_BASE,

BF_IOMUXC_UART3_UART_RX_DATA_SELECT_INPUT_DAISY(BV_IOMUXC_UART3_UART_RX_DATA_SELECT_INPUT_DAISY_AUD_RXC_ALT2)); /* Input Select (DAISY) Field: Selecting ALT2MUX Mode Select Field. mode of pad AUD_RXC for UART3_TX_DATA. */

That's the same settings I have been using.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jaya Kumar,

My apologies. I checked with the Pins Tool and the alternative you mention should work correctly. I had tested it and there is a conflict with certain configurations but the one you mentioned looks valid according to the Pins Tool. It should work correctly.

I hope this helps!

Regards,