- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- KL03: Problems with TPM Running off OCERSCLK when Core Clock is Internal

KL03: Problems with TPM Running off OCERSCLK when Core Clock is Internal

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have the TPM module running off the OCERSCLK from an exterior crystal at 6.144MHz. When I have the core clock set to run off the same crystal, my TPM output is perfect, exactly as I expect. When I change the Core Clock to 3MHz HIRC internal clock, the TPM output looks pretty close to normal, although it seems to be slighly affected by the clock change. When I change the Core Clock to 2MHz LIRC, the TPM output is not normal at all. Channel interrupts occur out of the blue when they shouldn't and the counters do not appear to be counting properly. When I change the Core Clock to 8MHz LIRC, there is no TPM output at all. Any idea what is causing this?

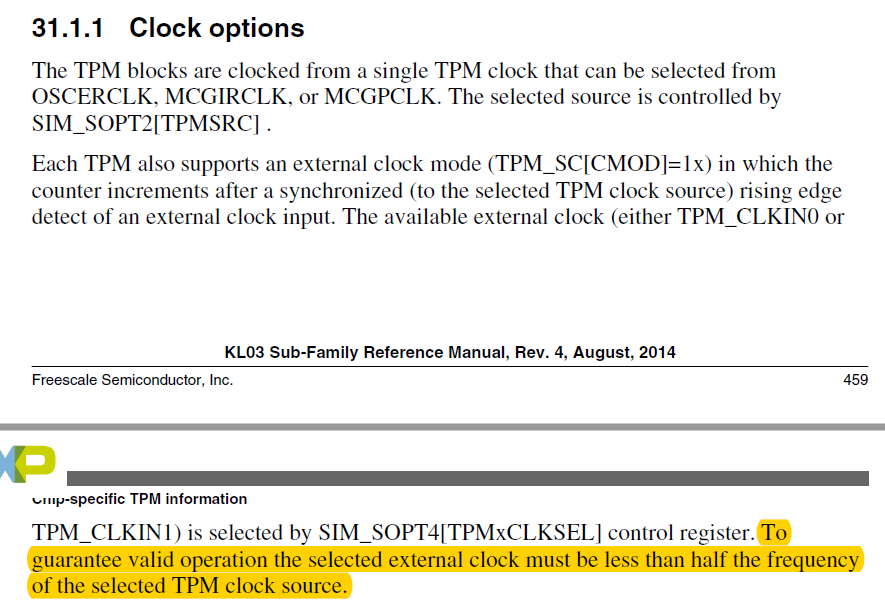

When I read through the user's manual, the best I could find is the excerpt below.

Could my core clock be causing problems with the TPM module in a similar manner to the external clock mode even though I'm not using the external clock mode? If so, how? I thought that the TPM module would be isolated from the core clock since it is running off it's own clock. Is there a rule-of-thumb for this?

Thanks,

Sara

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sara,

The bus clock and the TPM counter clock do not need to be the same clock source.

Could you change a browser and check if could find that attachment: Thanks.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ma,

I'm not sure that you understand my problem. My timers are running off an external 6.144MHz clock that is being brought down to 307.2kHz for TPM1 (PWM) and 19.2kHz for TPM0 (BPSK). When I run the core clock off the same external clock (6.144MHz) everything works fine. However, when I change the core clock to be internal HIRC 3MHz or LIRC 8MHz and LIRC 2MHz (no changes to the timer clock) it does not work properly. It is especially bad at LIRC 2MHz, the interrupts are not happening at the right times. SO...the timers are still running off the external clock...I have only changed the core clock.

I'm trying to understand why this is. I'm guessing that it has something to do with the bus clock since the bus is what clocks the interrupts correct? So, even though the timers are running independently with an external clock, they are still affected by the core bus clock. Is there a rule of thumb here? Should the bus clock be related to the timer clocks in some way so as to keep them synchronized properly?

Also, you said that you had attached your code, but I didn't get the attachment. Can you resend it?

Thanks,

Sara

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sara,

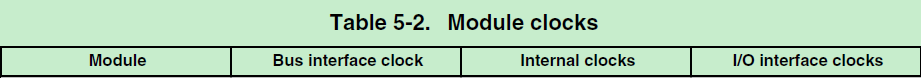

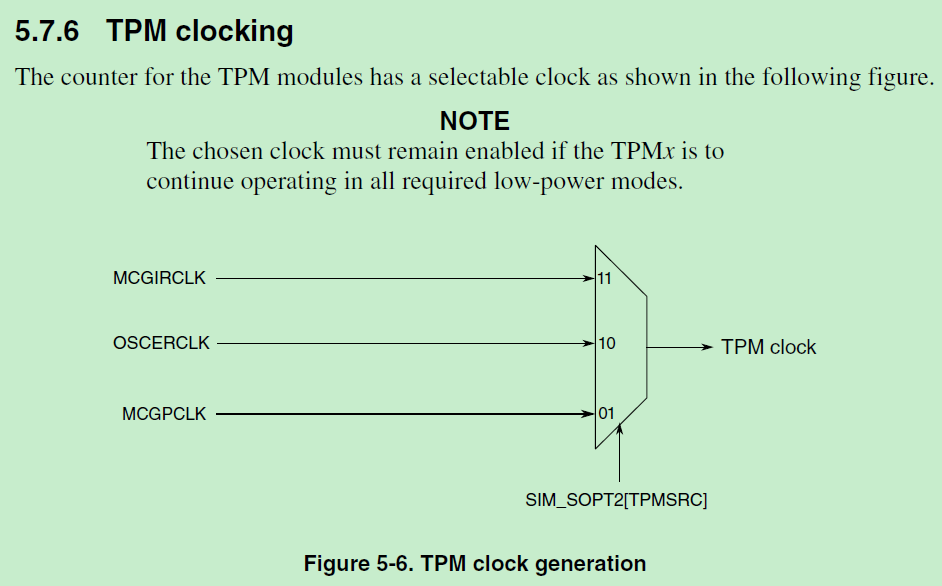

The KL03 reference manual shows the module clock source:

The Bus clock for TPM module interface clock, core using bus clock to access TPM module registers.

The TPM clock below is for TPM counter clock source:

From my point, if the core/bus clock using KL03 internal clock source, the TPM interrupt generation could not be affected. Your mentioned behavior is quite strange.

Please check attached my test software code.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ma,

Yes, I am familiar with these tables from the manual. So, if I understand you correctly, the bus clock and the TPM counter clock do not need to be the same? I don't read that from the tables.

Also...there is no attachment of your code. Can you resend?

Thanks,

Sara

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sara,

The bus clock and the TPM counter clock do not need to be the same clock source.

Could you change a browser and check if could find that attachment: Thanks.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hui,

I got the attachment, you were right, changing the browser made a difference.

I believe I have sorted out my problem. My interrupt routine was taking too long when I slowed down the core clock. After cleaning up the code in the ISR, I was able to get things working with the slower internal clocks.

Thanks for your help!

Sara

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you let us know which mode of TPM module you are using?

I tested the TPM module with Edge-Aligned PWM mode, if the PWM signal output based on the TPM counter clock frequency vs. PWM signal frequency.

For example, if I using the IRC48M clock as TPM counter clock, I only could generate the PWM signal with 12MHz 50% duty cycle.

The bus clock frequency (I test the bus clock at 8MHz or 24MHz) doesn't affect the PWM signal output.

Customer doesn't using the TPM module with external clock mode. The TPM external clock mode, the TPM counter clock is from TPM_CLKIN0 or TPM_CLKIN1 pins.

Thank you for the attention.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I’m using TPM1_ch0 in edge aligned PWM mode, triggered by the TPM0 overflow. TPM0_ch0 is set in software compare mode. The intent is to shift the phase of TPM1 whenever the channel interrupt occurs on TPM0 to create a BPSK signal. I have both TPM timers running off an external 6.144MHz crystal via OSCERCLK. I am not using the external clock mode that requires TPM_CLKIN0 or TPM_CLKIN1 pins.

This works perfectly when I run the core clock off the same external Crystal. I use the following code for this:

//Set up the Run Clock MCGOUTCLK at 6.144MHz from crystal via OSCCLK

MCG_C1=0b10000000; //Set the external clock as the main clock mode (10), disable the LIRC

MCG_C2=0b00000000; //External clock requested

MCG_SC=0b00000000; //Set the FCRDIV=000 for division factor=1

MCG_MC=0b00000000; //Set the low-frequency internal reference clock divider=000 for division factor=1 (not using this), Disables HIRCEN

SIM_CLKDIV1=0b00000000000000010000000000000000; //Sets bits 31-28 as Outdiv1=0000 (/1), Outdiv4=001 (/2)

//Start-up the external crystal for the core clock

GPIO_WR_PSOR(GPIOA, 1U<<8); //Set pin8 on PortA to turn on external crystal

GPIO_WR_PSOR(GPIOA, 0U<<9); //clear pin9 on PortA to make it active

OSC_BWR_CR_ERCLKEN(OSC, 1); //Enables the external reference clock (OSCERCLK)

OSC_BWR_CR_EREFSTEN(OSC, 1); //Controls whether or not the external reference clock (OSCERCLK) remains enabled when the MCU enters Stop mode (0) disables, (1) enabled

However, when I change the core clock to one of the internal clocks (3MHz HIRC, 2MHz LIRC, 8MHZ LIRC), the timers do not quite work properly. This is especially noticeable for the 2MHz and 8MHz internal core clocks. I thought that the timer module would be independent of the core clock when it is running off an external clock. This is obviously not true. So…what affects it? Does the bus clock have anything to do with the TPM generation? It seems from the User’s Manual that the bus clock clocks the peripherals. How does this work?

Any help you can provide would be great!

Thanks,

Sara

Sara Stout-Grandy, M.Eng., Ph.D., P.Eng.

Senior Hardware Designer

20 Angus Morton Dr., Bedford,

NS, Canada, B4B 0L9

902-450-1700, x278

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

First of all, I am sorry for the later reply.

I do a test at FRDM-KL03Z board, using TPM1 module channel 0 at output compare mode, which enable the TPM1 timer overflow interrupt.

The TPM0 module channel 0 works at edge aligned PWM mode, which was triggered by TPM1 overflow.

The TPM1 overflow interrupt service routine, I am using the TPM driver to modify the TPM0_CH0 PWM signal frequency.

The KL03 MCG module is using internal IRC8M as clock source:

Core clock frequency is 8MHz;

Bus clock frequency is 2MHz;

TPM0/1 clock source is IRC8M, frequency is 8MHz.

I could get the TPM0_CH0 PWM output frequency modification at TPM1 overflow interrupt service routine.

I attached my test code for your reference.

The test code is based on KDS V3.2.0 IDE software with Processor Expert tool.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------