- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- C293 custom board ready signal stay low issue

C293 custom board ready signal stay low issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

C293 custom board ready signal stay low issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

we have made a custom board base on C290PCIe_RDB Rev B version, the same DDR3 chip, the same CPLD hardware type. even we programmed the same cpld file using oamp-v2.2 version.

after power on , we got the asleep and ready waveform as attched picture showed. it is very strage the asleep signal seem ok, but ready signal is strage.

Is the power on sequence issue or wrong por config issue? need your urgent help, thank!!!!

by the way the IFC_CLK0 signal is normal 50MHZ as the RDB board tested.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Both READY and ASLEEP negated means the core is in power-saving mode (doze or nap).

In other words, the core is not "full on", but in halted mode. After reset, the core may be held in "halt" mode if, for example, boot sequencer is used.

Have a great day,

Alexander

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, Alexander:

thanks for your reply!!!

It seem the C293 core always in "halt" mode since power on. The boot sequencer now set to default, which means the boot sequencer is disabled. No I2C ROM is accessed.

how can we set the C293 core in "full on" mode?

I check all the power supply, all the Power-on reset sequence, all the POR configuration, they are all correct, exactly the same POR configuration with the C293Pcie-RDB. Why the RDB borad ready singal can assert while our new board ready singal is negation?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The core may be in "halt" mode if "cfg_cpu_boot" is sampled low at reset. Please look C29x Reference Manual, Section 4.5.4.15 for details.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, Alexander:

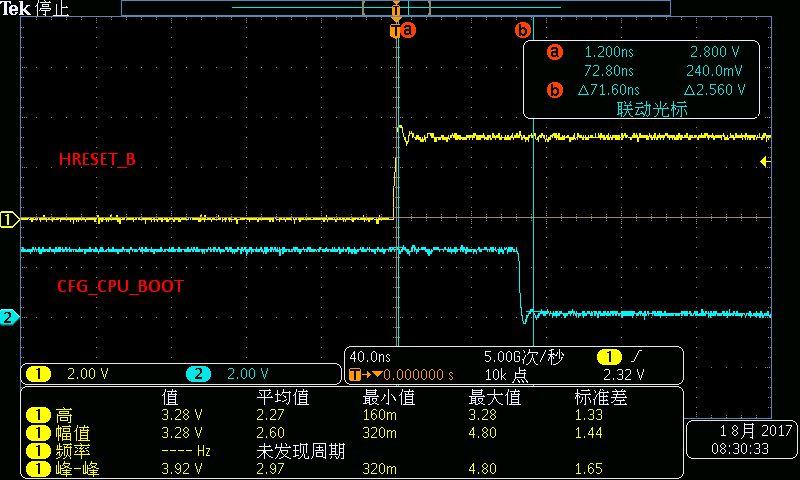

We have checked all the POR configuration, all the power supply. "cfg_cpu_boot" is sampled high at reset , please see the attchment picture.

Which factor would affect C293 in halted mode if POR configuration is correct? thanks!!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. You said "we have made a custom board base on C290PCIe_RDB Rev B version" - please specify the exact (full list) of differences between your board and C290PCIe_RDB.

2. You said "We have checked all the POR configuration" - please submit me POR values you are using.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to your schematic, configuration pin cfg_ddr_speed[1] is not pulled down - resistor R541 is "NC"

However, according to por_config scope screenshots, configuration pin cfg_ddr_speed[1] is driven "low" at reset.

According to C29x Reference Manual, Table 4-25, this "low" value is incorrect for given combination of DDR clock ratio and cfg_ddr_speed[0] settings.