- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Having trouble with PIT->PDB->ADC->DMA on K22

Having trouble with PIT->PDB->ADC->DMA on K22

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Having trouble with PIT->PDB->ADC->DMA on K22

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm on CodeWarrior 10.7, using Processor Expert (at least for some parts) and writing code for an MK22FN1M0, and I'm having a heck of a time getting the PDB to work right with the ADC.

My goal is to sample periodically from two ADC channels and place the results in two separate circular buffers via DMA. The sample rate for the two channels is the same but they're effectively independent and the timing relationship between them is not critical.

I think the way this ought to work is to have the PIT running at the 16 kHz sample rate trigger the PDB, with the PDB in one-shot mode generating the triggers for the ADC's A and B channels in sequence.

I've got the PIT running at the appropriate rate and I can see from the PDB interrupt that the PDB is running correctly. I've been able to get a few samples out of the ADC but then I get a sequence error and everything stops.

The documentation is scattered and unclear, and I'm seeing other posts here suggesting that maybe the PDB's sequence error flag clearing is just plain broken. The manual says that a sequence error means that the last conversion was not completed before the next trigger occurred, but I'm getting errors when the conversion time is 4 us and the interval is 4000 us.

It looks to me like maybe the sequence error depends not on whether the conversion is still in progress, but whether the value has been read from the result register yet. Is that correct?

What is the recommended DMA setup to get both result registers at the appropriate time and put them into separate buffers? The ADC's DMA trigger is common to both A and B channels and I can see several possibilities, but there must be a standard solution for this. Is there a working example somewhere that uses the PIT, PDB, ADC, and

DMA together?

Thanks,

Scott

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The PDB couldn't trigger the ADC module, when that ADC module still in conversion process.

There are some similar application for your reference:

DMA + ADC + PDB with Processor Expert (Kinetis K22 - MK22FN512VLH12)

https://community.nxp.com/message/435451?commentID=435451#comment-435451

Due to the PDB using ping-pong mode to tigger the ADC A/B conversion.

Each ADC conversion finish will trigger the DMA transfer, it will be better to do ADC data transfer after both ADC A/B conversion done.

For the ADC0_RA & ADC0_RB with the continue address, using the PDB interrupt to software trigger DMA to transfer both ADC conversion data will be more effective.

Thank you for the attention.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The PDB couldn't trigger the ADC module, when that ADC module still in conversion process.

I understand that, but it looks like the sequence error is generated when the result register has not been read and not just when the conversion itself is still in progress. Is that correct? Because I have it working now without changing my PDB timing and just being careful about my DMA setup to make sure that the result register is always cleared.

My solution to get it running was to use the PDB's interrupt timer to generate a DMA trigger after the completion of both ADC conversions. The first DMA channel saves RA to a buffer and chains to a second channel that saves RB to its buffer. Both channels are set to destination modulo mode with minor and major counts of 1. I was also able to eliminate use of the PIT, since the PDB itself is able to give me what I need for the sample clock.

Due to the PDB using ping-pong mode to tigger the ADC A/B conversion.

Each ADC conversion finish will trigger the DMA transfer, it will be better to do ADC data transfer after both ADC A/B conversion done.

I'm having some trouble parsing that. The first statement is a sentence fragment. I think what you're saying is that with the PDB in back to back mode, each conversion triggers the DMA transfer and therefore it would be better to do the data transfer after both conversions are done. Is that correct?

It was not obvious to me from the documentation how the single DMA trigger would be done, but using the PDB interrupt counter seems to have been the correct answer, or at least one correct answer.

Thanks,

Scott

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scott,

I find below thread about PDB channel sequence error:

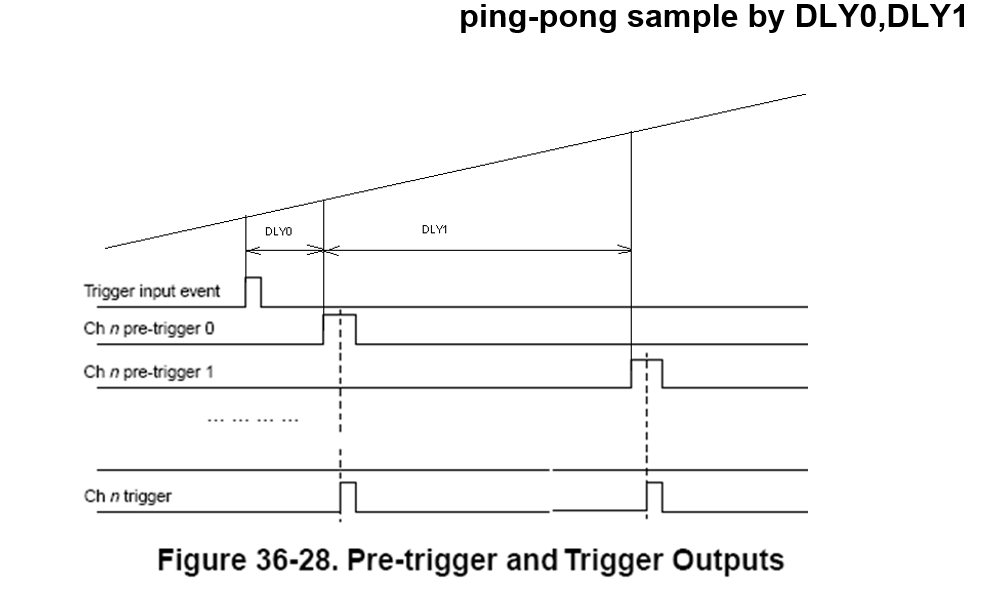

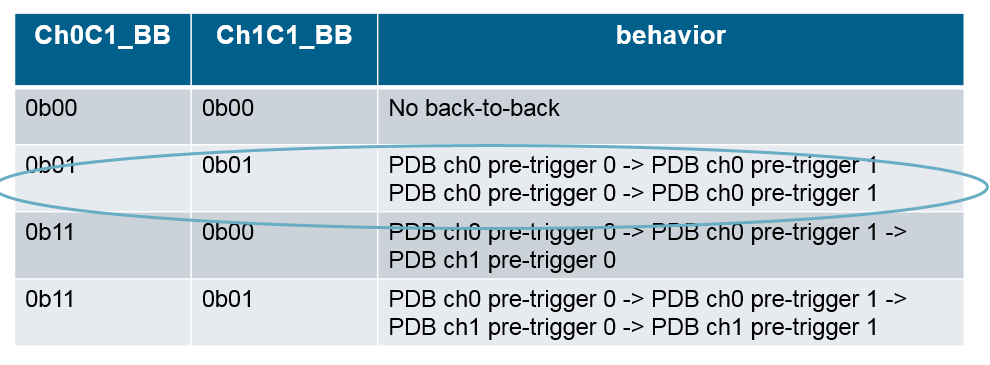

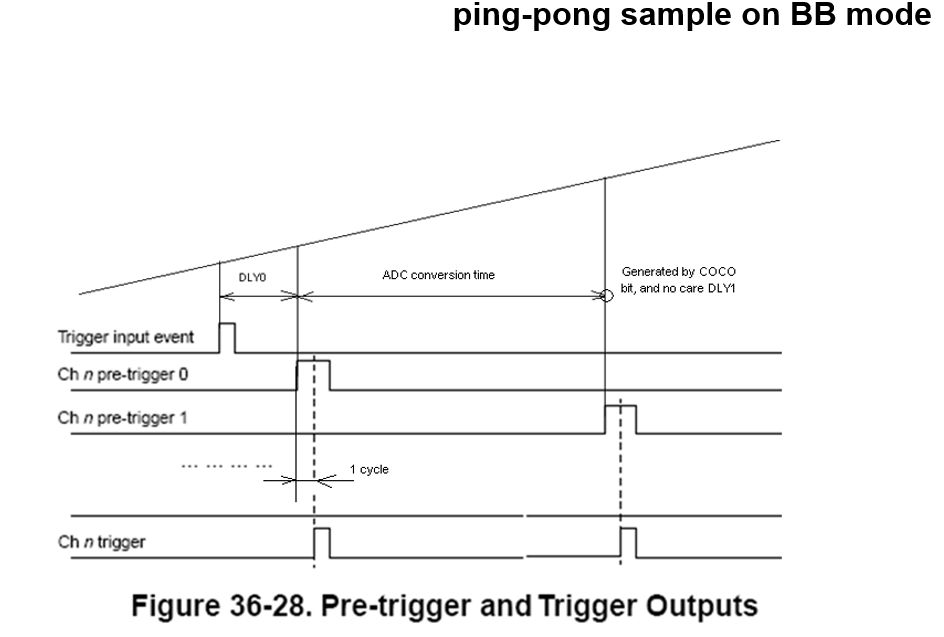

There are two types of ADC working way in ping-pong mode, please check below picture for the detailed info:

Type 1: using two PDB pre-trigger of PDB channel:

Type 2: using back-to-back mode:

Thank you for the attention.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. I think what was throwing me off was the description of the sequence error in the manual:

Sequence error detected on PDB channel's corresponding pre-trigger. ADCn block can be triggered

for a conversion by one pre-trigger from PDB channel n. When one conversion, which is triggered by

one of the pre-triggers from PDB channel n, is in progress, new trigger from PDB channel's

corresponding pre-trigger m cannot be accepted by ADCn, and ERR[m] is set. Writing 0’s to clear the

sequence error flags.

And later:

A sequence error typically happens because the delay m is set too short and the pre-trigger m asserts

before the previously triggered ADC conversion finishes.

Both of these only describe the conversion being in progress and make no mention of clearing the COCO bit. A more accurate description of the sequence error bit (top quote) would have saved me some trouble.

Thanks,

Scott

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scott,

I agree, the reference manual need to provide more detailed info.

I will forward related info to Kinetis product team. Thanks.

best regards,

Ma Hui