- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Variation in number of cycles for Load/Store in different memory regions?

Variation in number of cycles for Load/Store in different memory regions?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Variation in number of cycles for Load/Store in different memory regions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello to all,

I am considering Load and Store instructions for different memory regions and wanna analyzed their respective effect in the energy-consumption. From my script:

"STR.W R6,[R0]\t\n"

"STR.W R6,[R0]\t\n"

.

.

.

"STR.W R6,[R0]\t\n" (1000times as interrupt)

and on the basis of the value of R0 register, the number of cycles are varying. For an example:

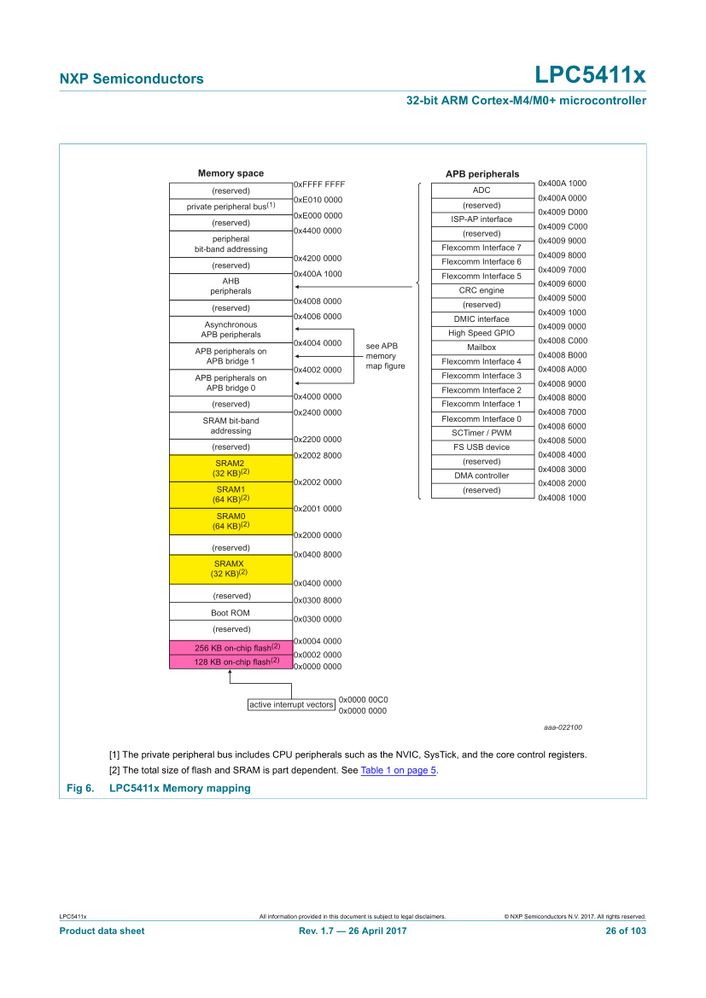

SRAMX Memory Location: LDR R0,=#40000002 ; => Number of cycles: 8

SRAM0 Memory Location: LDR R0,=#20000002 ; => Number of cycles: 2

SRAM1 Memory Location: LDR R0,=#20010002 ; => Number of cycles: 2

SRAM2 Memory Location: LDR R0,=#20020002 ; => Number of cycles: 2

This is what the result I am getting. And if in the case of accessing the instructions with offset, will show a huge change in the number of cycles up to 12 cycles each instruction.

Along with that, while trying to access the Flash memory there is no detection of the interrupt.

Can any body explains me such behavior??. Also, kindly find the attached memory map.

My target board is LPC 54114 and my target processor is ARM Cortex-M4.

Thanking you,

Regards,

Himanshu Doshi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The change of the number of cycles from the same instruction when you are trying to get access to different memory areas, it is related, to the architecture of the device, since there is a CortexM4 and CortexM0 , not all the memory can be access in the same way. This is reflect in the latency response of the instruction and the one that take the most, it is the one related to the AHB cross Bar, that need to validate that you have the credetencials to access

For sure this is a expected behavior.

Have a great day,

Soledad

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hii Solebad,

First of all thank you very much for your reply. Yes, I understood your point, that accessing different memory regions resultant into latency response of the instruction and it's the major one for the more number of cycles. But, now I have two small issues to mention:

1. As mentioned in my original post, the number of cycles during the memory access SRAMX is way higher than the others. But, in some documentation, I have read that the cycle count/energy consumption is more when the memory location is far from the flash or in other words, farthest location memory access consume more. And from the architecture, the SRAMX is near to flash, then also why such behavior?

2. Why the relative energy consumption between two instruction varies. For example: If I access sequence of NOP instruction before and after LOAD or STORE instruction. Then, the expected energy consumption should be higher for LOAD/STORE compared with NOP. But, during different memory access, it varies, sometimes it becomes lower than NOP instruction, which is quite unexpected. Can you please tell me why such behavior??

Thank you very much once again,

Regards,

Himanshu