- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- ENET1_TX_CLK pin setting for RMII function of i.MX6ULL

ENET1_TX_CLK pin setting for RMII function of i.MX6ULL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all,

We want to use ENET1 as RMII function.

In this case, we have a question about pin setting of Reference Clock.

<Question>

When I use a reference clock for RMII, how should I set ENET1_TX_CLK?

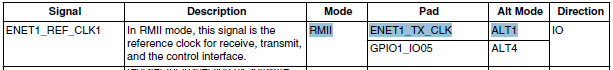

There is a different description about ENET1_TX_CLK pad in Reference Manual.

IMX6ULLRM Rev. 0, 09/2016:

- Table 23-1. ENET1 External Signals(P.950)

I seem that ENET1_TX_CLK pad is set to ALT1(ENET1_REF_CLK1).

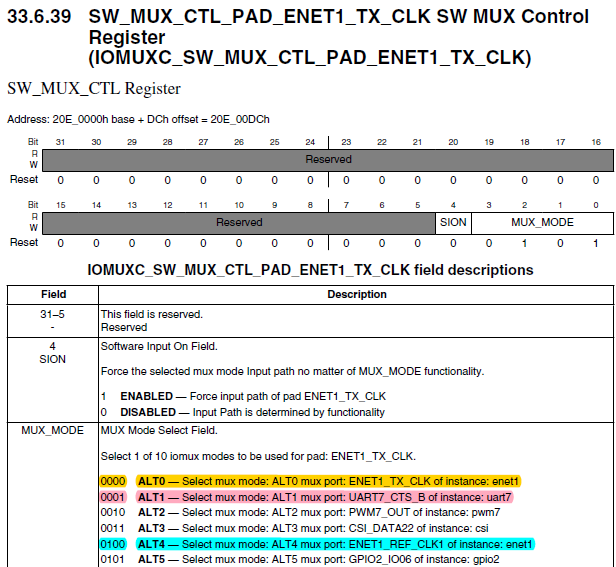

However, in IOMUXC_SW_MUX_CTL_PAD_ENET1_TX_CLK description, ALT1 is UART7_CTS_B setting.

IMX6ULLRM Rev. 0, 09/2016:

- 33.6.39 SW_MUX_CTL_PAD_ENET1_TX_CLK SW MUX Control Register (IOMUXC_SW_MUX_CTL_PAD_ENET1_TX_CLK) (P.1580)

Here, I seem that ENET1_TX_CLK pad setting for ENET1_REF_CLK1 function is ALT4.

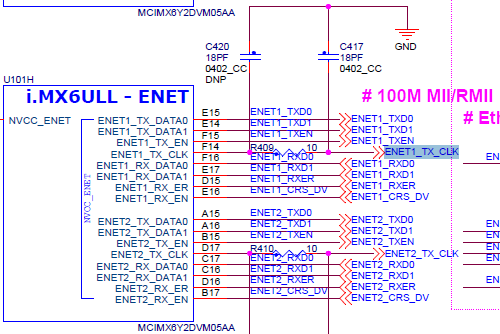

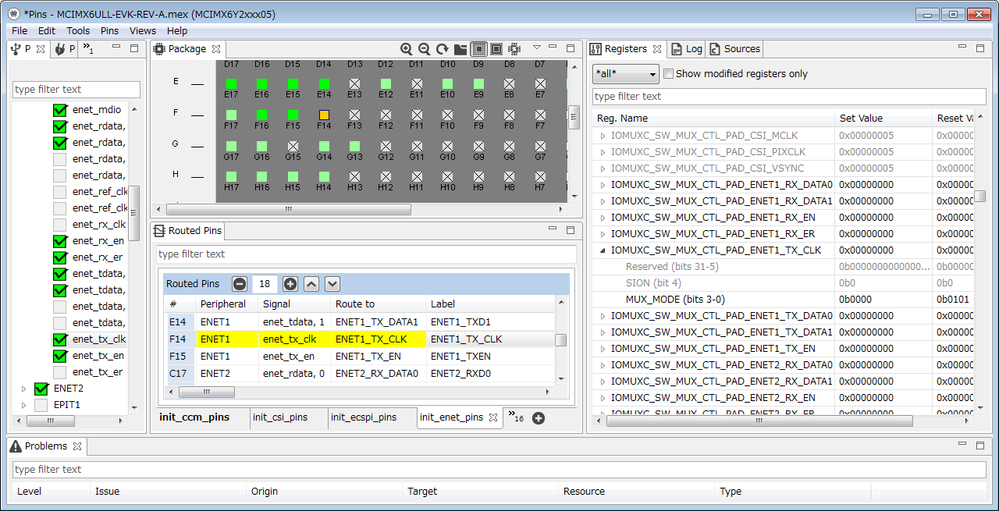

In addition, accoding to the schematic for RMII of MCIMX6ULL-EVK(CM) and PIN tool(V3.0.2) for MCIMX6ULL-EVK-REV-A,

ENET1_TX_CLK(F14) pin is used as ENET1_TX_CLK signal.

I am confused.

About a reference clock for RMII, please tell me the right setting.

Best Regards,

Yuuki

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

ENET1_TX_CLK is used as ENET1_REF_CLK1 (ALT4 mode) in the reference design..

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

ENET1_TX_CLK is used as ENET1_REF_CLK1 (ALT4 mode) in the reference design..

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------