- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- IMX7D power saving mode result

IMX7D power saving mode result

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMX7D power saving mode result

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Support,

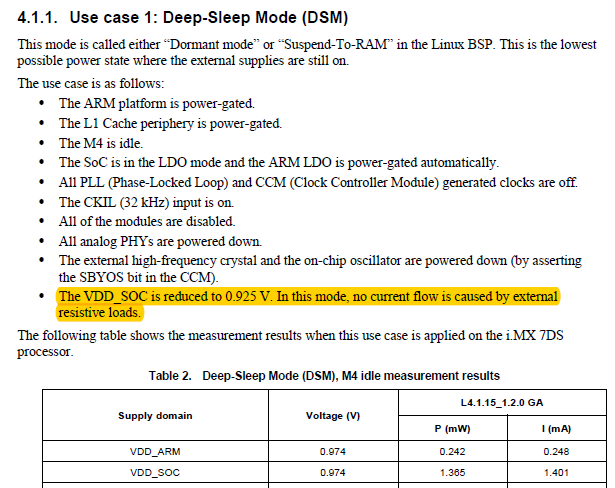

1. DSM mode

We are trying to get some testing data on DSM mode description in AN5383. We set "echo mem > /sys/power/state" and measure the result. Each power rail to IMX7D pins look well except the VDD_SOC that is still about 60mA. Seems the VDD_SOC is not in the right idle mode. How do we check it?

2. normal mode

After power on, the system will run system idle mode when no thread, we can see the VDD_ARM is about 5mA, it's acceptable for us, but we found the VDD_SOC is about 200mA. It's so large and just like we run 100% on M4 processor but we do nothing. How do we check it?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

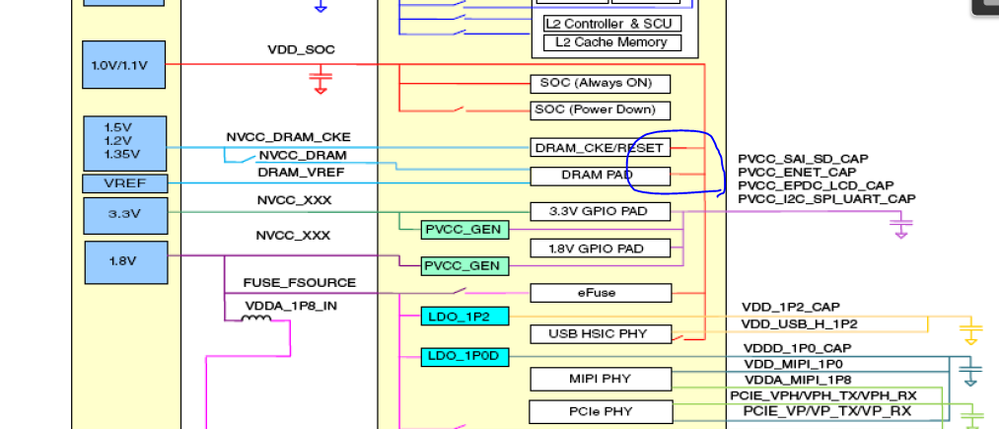

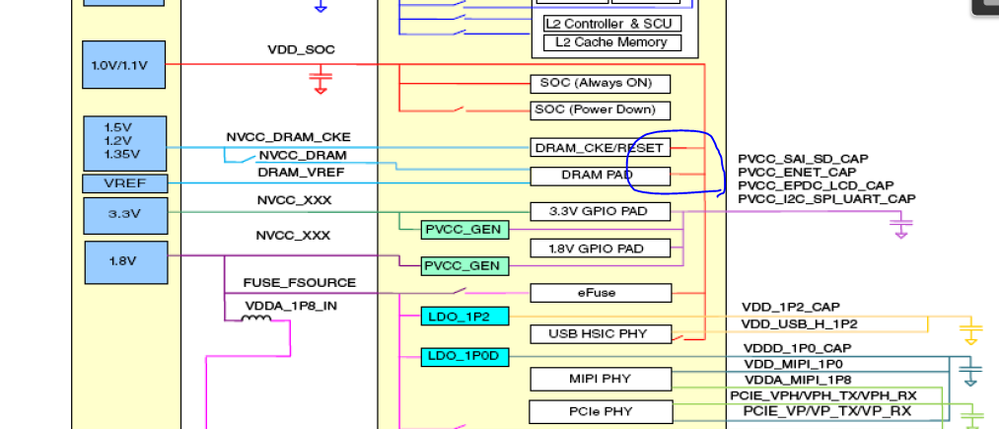

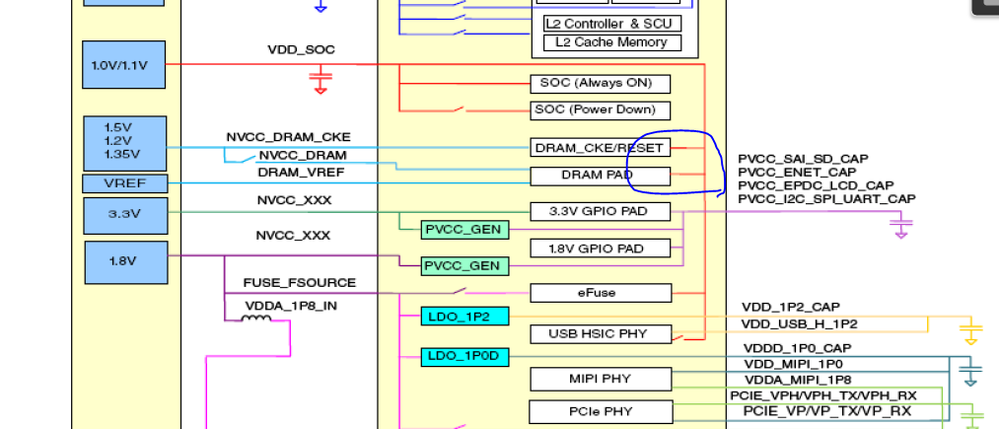

It seems no relation between DRAM pad and VDD_soc, does the power block have wrong connection from VDD_soc to DRAM pad? We just want to find anything related to VDD_SOC to find out the low power mode setting root cause the difference from the Saber board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

seems warp7 uses lpddr3 so one can look at it

http://www.element14.com/community/docs/DOC-79058

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

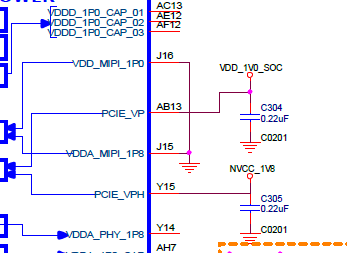

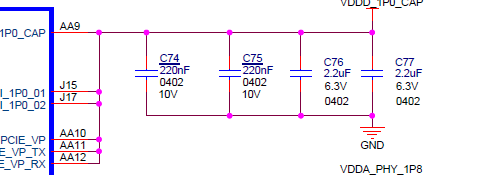

Back to the original question, does VDD_SOC related to the DRAM pad shown in the below picture? How do we check it since we can not see relation in the schematic?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

for power associated with pad please refer to Table 100.

i.MX 7Dual 19 x 19 mm functional contact assignments i.MX7D Datasheet

(column Power Group)

http://cache.nxp.com/files/32bit/doc/data_sheet/IMX7DCEC.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

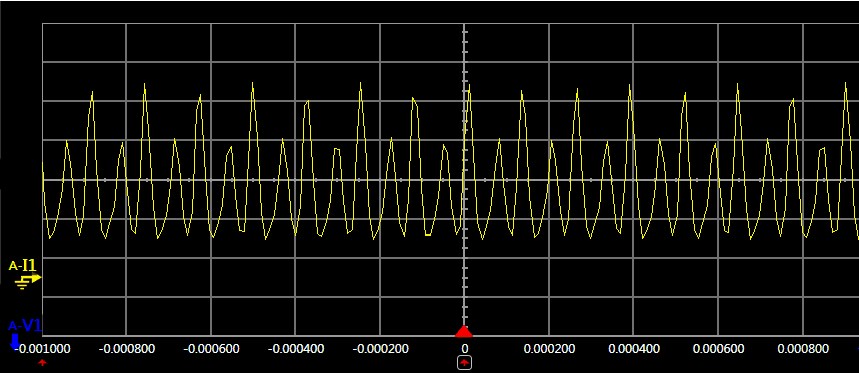

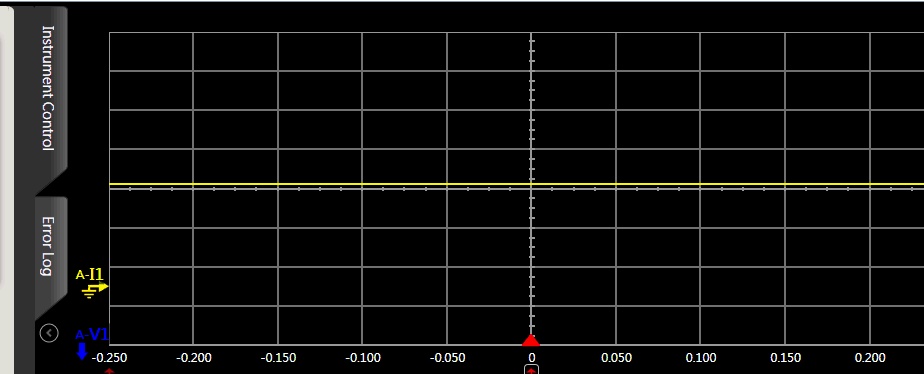

We are also investigation that the VDD_SOC power consumption behavior, please see the below two picture. The VDD_SOC is measure under u-boot. You can see there is big difference between Saber board and our board. Our SW mentioned that the setting and configuration difference is DRAM setting that Saber uses DDR3L but our board use LPDDR3. Does the DRAM configuration impact the VDD_SOC current draw? In the power rail block of the IMX7D, the VDD_SOC seems to be related to DRAM PAD. Does NXP have LPDDR3 setting sample for us to refer it?

Saber board VDD_SOC

Our board VDD_SOC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

you are right, since reference board uses DDR3L but your board use LPDDR3,

behaviour may be completely different, so board may behave weirdly.

You should use settings and configuration for some lpdrr3 reference board

for example for imx7d-12x12-lpddr3-arm2

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How do we get the reference board/schematic and source code? Has it been released?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I beleive it is not publicly available, for LPDDR3 MC32PF3000A2EP

should be used, for DDR3L - MC32PF3000A1EP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We also use VDD_SOC to supply the PCIE_VP which is used for BDSL support, is it possible to be a issue for losing power when set to low power mode?

The NVCC_1V8 also supplies to PCIE_VPH for BDSL support and the NVCC_1V8 can keep to save power without additional loss.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- one can look at Chapter 21 Low-level Power Management (PM) Driver

attached Linux Manual for sources low power driver.

- VDD_SOC should be 0.95V according to Table 9. Operating ranges

i.MX7D Datasheet

http://cache.nxp.com/files/32bit/doc/data_sheet/IMX7DCEC.pdf

>We also use VDD_SOC to supply the PCIE_VP which is used for BDSL support, is it possible

>to be a issue for losing power when set to low power mode?

I believe yes. To be sure suggest to disconnect and connect as it is done on i.MX7D SabreSD schematic.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In An5383, it shows the VDD_SOC will reduce to 0.925V, is it wrong?

>We also use VDD_SOC to supply the PCIE_VP which is used for BDSL support, is it possible

>to be a issue for losing power when set to low power mode?

I believe yes. To be sure suggest to disconnect and connect as it is done on i.MX7D SabreSD schematic.

--It's a bad news for us that we do not have 0 ohm to the PCIE_VP. The NVCC_1v8 also connects to PCIE_VPH for the same purpose with PCIE_VP but the NVCC_1V8 can have ultra low power consumption when set to DSM. It the VDD_SOC will still have high current on DSM mode due to PCIE_VP, the NVCC_1V8 should have similar result but it does not. Do you have any idea to disable the related function used for PCIE_VP to check if we can let the PCIE_VP to stop to sink the current for VDD_soc?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes, it is misprint. Correct value is given in Datasheet.

Regarding PCIE_VP connections probably you can imitate behaviour on SabreSD board.

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

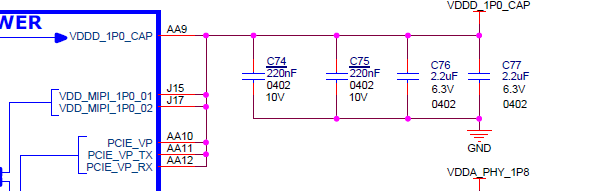

1.So, the VDD_SOC power = 0.975V will not be changed whatever the M4 stay idle or active or high loading mode?

2. In Saber board, the net connect to VDDD_1p0_cap, it seems that we can not supply the VDD_soc to the PCIE_VP directly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- according to sect.4.1.1. Use case 1: Deep-Sleep Mode (DSM) AN5383 :

- the M4 is idle.

- you can measure VDDD_1p0_cap on SabreSD board in DSM mode

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We use Saber board to do the experiment, we check the internal LDO VDDD_1P0_CAP power rail will be disabled and we supply external 1.0V to supply the below power rail and found the there are extra current flow to this power power rail about 20mA. The VDD_SOC on our board has 65mA, if we remove this additional 20mA, there is 44mA which is still loss in the system in suspend mode. Do you have any idea for it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Franky

since VDDD_1P0_CAP power is applied in your case, it may

influence on other processor power rails (domains), causing bigger currents

form them, due to parasitic voltages leaking from powered VDDD_1P0_CAP block

to other processor power domains.

Unfortunately there are no estimations for such additional power consumption.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

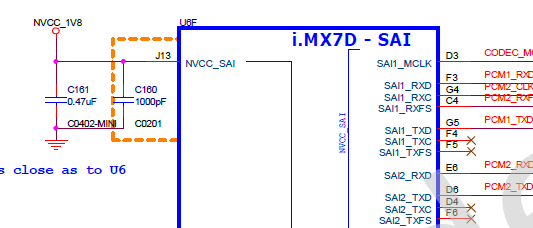

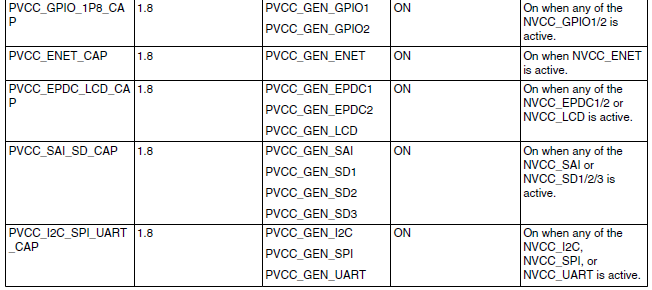

Hi Igor, we are also checking the additional power consumption on I/Os, I mean NVCC_1V8 and NVCC_3V3 to supply the NVCC_xxxx for I/O power as below:

Since we do not leave 0 ohm here but we can still measure some current on NVCC_1V8. Except these NVCC_xxx, we has disconnected the power connection for all peripheral devices. So, it seems there is still some power going into the power pins as show below when we go into DSM mode.

My question is, do we need to turn off the data bus before we excuse the DSM command? Or the DSM will auto turn off the I/O operation to save the power?

Does this power rail for NVCC_xxx have chance to consume power more than 10mA?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Franky

please check Table 5-4. Power Mode i.MX7D Reference Manual

http://cache.nxp.com/files/32bit/doc/ref_manual/IMX7DRM.pdf

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

To turn off the integrated PMU before enter the DSM mode since they are all on in default?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

most voltages are ON, but almost all modules are disabled. Its clocks are turned off.

You can measure voltages on nxp i.MX7D Sabre reference board.