- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- KL16 and I2S peripheral: question on the positioning of the SYNC field in the TCR2 register.

KL16 and I2S peripheral: question on the positioning of the SYNC field in the TCR2 register.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

KL16 and I2S peripheral: question on the positioning of the SYNC field in the TCR2 register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everybody,

I am using a KL16 microcontroller for communicating with another device via the I2S interface. The KL16 is configured as a slave and is intended to send audio data to the other device, which will generate both the frame clock and the bit clock.

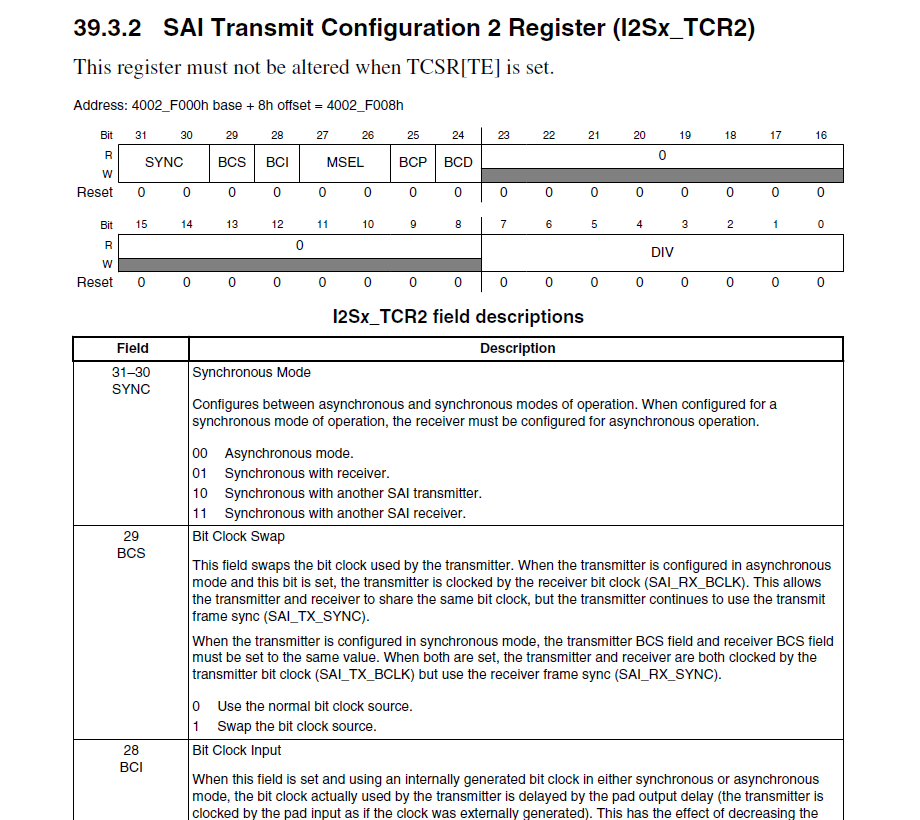

According to the reference manual, in this scenario the SYNC field of the TCR2 register must be set to 01 (Synchronous with the receiver).

The manual (rev. 3,3) also reports that this field is located at the bits 30 and 31 of TCR2 (see section 39.3.2).

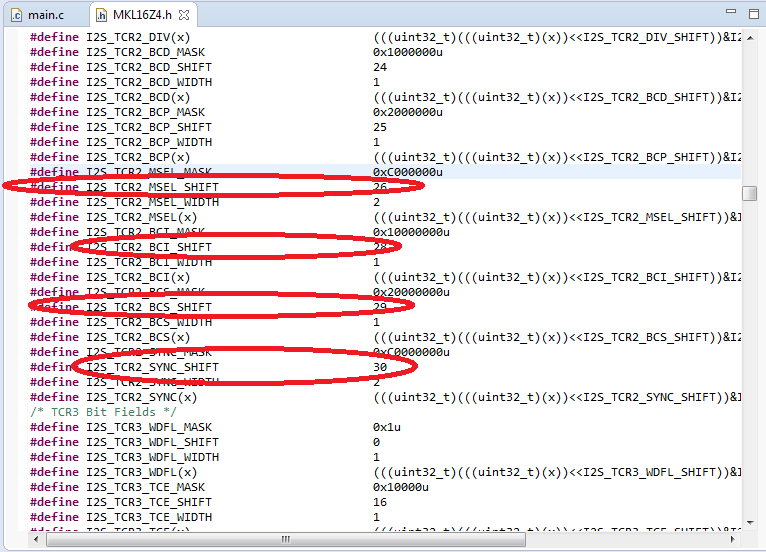

On the other hand, the MKL16Z4.h file reports that this field is located at the bits 26, 27. Also, in this file the fields BCS, BCI and MSEL are not mentioned at all.

Now, by properly setting bits 26 and 27 rather than bits 30 and 31, I was able to successfully initialize and make I2S work. So, it seems that the manual is reporting a wrong piece of information. Therefore, I would like to know:

- the real content of the TCR2 register

- if there is some other register of the same peripheral whose documentation is misaligned with the real content of the register.

Thanks and best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear XiangJun,

I get back to you hoping that you can help me again with another issue relevant to the I2S peripheral of the KL16 microcontroller.

The peripheral is configured as a slave and is connected to a master device which drives SAI_TX_BCLK and SAI_TX_SYNC signals and gets data from the SAI_TX_DATA pin.

The SAI_TX_BCLK is a 256kHz square wave (active high)

The SAI_TX_SYNC is an 8KHz square wave, active high and whose rising edge is aligned to the 1st bit of the 1st word.

The data sent to the SAI_TX_DATA pin are composed of 2 words, each of 16 bits. The 1st word is set to 0xAAAA, the 2nd one is set to 0.

Now, here is the issue: when the SAI_TX_DATA pin is physically connected to the input pin of the master, I can see that the waveform on this pin is different than the expected one. On the other hand, when the SAI_TX_DATA pin is NOT connected to the input pin of the master, the waveform on this pin is correct.

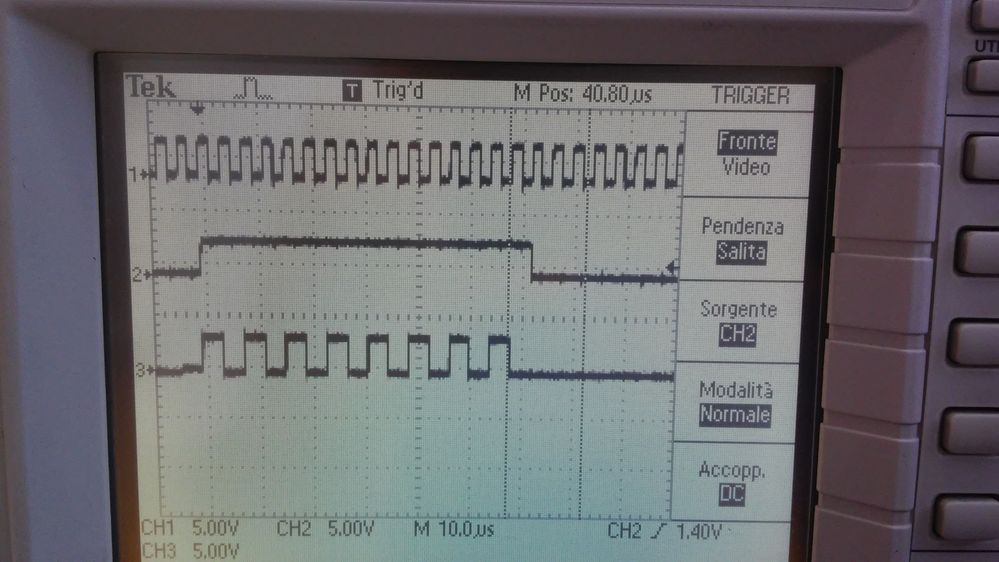

The first picture below (here trace 1 is SAI_TX_BCLK, trace 2 is SAI_TX_SYNC and trace 3 is SAI_TX_DATA) shows the 1st word correctly sent over the data line. This picture has been taken with the SAI_TX_DATA disconnected. from the input pin of the master device.

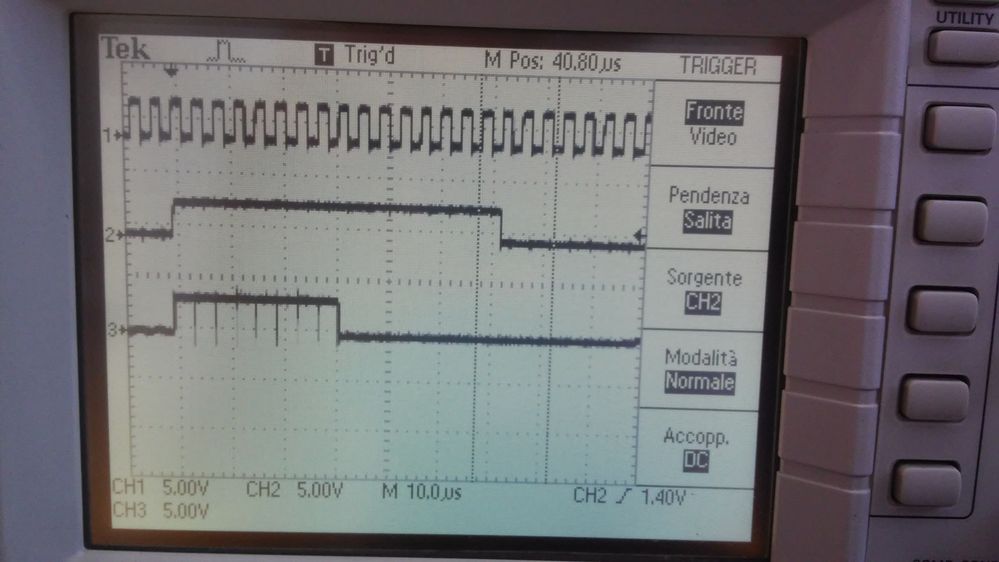

The second picture clearly shows the issue. Here, the peripheral behaves as though the "0" bits are transmitted in a very very short time.

Have you got an idea of what could be the cause of this behaviour?

Please, note that I also checked that the input pin of the master is actually configured as input and does NOT overload any signal connected to this pin.

Thanks in advance for your help.

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Nicola,

From the waveform of the second figure, I suspect that the master also drives the pad as you said, which means that the SAI_TX_DATA pin from Kl16 and master both drive the same signal, this must be avoided.

Pls test the master TX data pin, what is the result?

BR

xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello XiangJun,

actually the master TX data pin is left unconnected. The only connection is between the master RX data pin and the SAI_TX_DATA pin.

Also I want to highlight that, by looking at the two waveforms, in the wrong case the waveform sort of "shrinks" itself (all zeroes duration shrinks to almost nothing).

Thanks for now.

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear XiangJun,

thanks for your clarification. My application is only using the transmitter section of the SAI module. Therefore, the only signals which I intend to use are SAI_TX_BCLK/SAI_TX_SYNC/SAI_TX_DATA. Also, the SAI transmitter is a slave.

Then, SAI_TX_BCLK and SAI_TX_SYNC are generated by the remote device which wants to get audio data from the peripheral.

Now, my doubts stemmed from a misinterpretation of the following sentence (reported in section 39.4.3.1 "Synchronous mode"):

If the receiver bit clock and frame sync are to be used by both the transmitter and

receiver:

• The receiver must be configured for asynchronous operation and the transmitter for

synchronous operation.

Here, I misinterpreted the receiver as the remote device (whose bit clock and frame sync are inputs to the transmitter)

rather than the receiver section of the SAI module.

Finally, everything is clear to me and things are working as expected (and consistently with the documentation).

Thanks again for your help.

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Xiangjun,

thanks for your clarifications and for the file. Actually, I was using an older version (1.2) of the MKL16Z4.h which contained some piece of information regarding the fields of the TCR2 register not aligned with the contents of the reference manual.

At this point, though, it is still unclear to me why the register TCR2 must be initialized with the value 0x06000000 rather than 0x40000000 in order for the peripheral to work as expected. I did several tests and apparently the peripheral only works when bits 27, 26 are set to 0, 1. Honestly, this is puzzling me, since these bits should have no effect when the bit clock is externally generated (which is the case at hand).

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Nicola,

I do not know your application, do you use only transmitter of SAI module or both the transmitetr and receiver of SAI?

As you know that SAI module supports duplex transfer, in other words, the transmitetr and receiver supports asychronous mode, in the mode, the transmitter and receiver are independent.

transmitter signals:

SAI_TX_BCLK/SAI_TX_SYNC/SAI_TX_DATA

receiver signals:

SAI_RX_BCLK/SAI_RX_SYNC/SAI_RX_DATA

In synchronous mode of transmitter, both the receiver and transmitter share the bit clock and the frame clcok, in other words, the SAI_RX_BCLK/SAI_RX_SYNC are driven to SAI_TX_BCLK/SAI_TX_SYNC internally, the external pads signals SAI_TX_BCLK/SAI_TX_SYNC are not used.

For your case, you use synchronous mode of transmitter when the SYNC bits in I2Sx_TCR2 is configured as 01(Synchronous with receiver), the receiver is set up in asynchronous mode(the SYNC bits in I2Sx_RCR2 is configured as 00), as you have tried to set up, you have to use SAI_RX_BCLK/SAI_RX_SYNC as the bit and frame clock instead of SAI_TX_BCLK/SAI_TX_SYNC signals.

I suppose you only use transmitter with SAI_TX_BCLK/SAI_TX_SYNC/SAI_TX_DATA signals, in the case, you have to use asychronous mode with the SYNC bits in I2Sx_TCR2 configured as 00 in binary.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content