- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- eLBC P5040

eLBC P5040

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

eLBC P5040

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am working with the P5040 microProcessor and I have some questions.

P5040 eLBC has a 32 bits bus mixed data/address [LAD00..LAD31] but it also have 5 bits only for address: [LA27..LA31].

Does it means that I have a 37 bits address bus or just that LAD27..LAD31 are data only?

Another question I would appreciate it if you could answer me is about which are the bits that I should use if my device connected to the Local Bus has less address inputs. I have seeing some schematics where, if just 25 address bits are needed, [LA05..LA30] are used. That is something that I don't understand, shouldn't [LA00..LA24] have been used?

I hope you understand what I mean and someone could help me. Thank you in advance,

Paula

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. Both multiplexed LAD27...LAD31 and non-multiplexed LA27...LA31 are available in parallel and used to reflect the same address. You can use LAD27...LAD31 or LA27...LA31, this is up to designer. The difference between multiplexed and non-multiplexed address lines is in address phase (LALE cycle) required to change address on multiplexed lines, so sometimes using non-multiplexed addresses allows saving address phase cycles to speed up interface, for example in UPM-driven burst cycles.

2. We use opposite numbering scheme, LA31 is least significant address line for our processor. For 16-bit port size LA31 is "don't care", LA30 is least significant address line used for connection for 16-bit device. So, for 25 address lines this leads to LA05...LA30, where LA30 is lsb and must be connected to device' A0.

Have a great day,

Alexander

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry Alexander, one more thing.

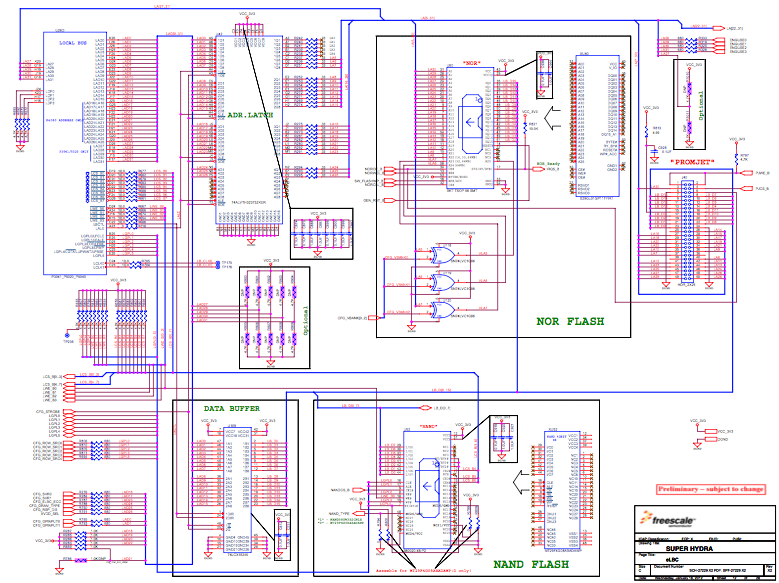

Ignoring the point about why not to use LA31, freescale Superhydra board has a 1 Gb NOR memory, which have 16 memory address bits and 10 memory sector bits, so this is 26 address lines. As you have told me, you have to use LA05..LA30, I guess the 16 LSB are the memory address and the other 10, the sector address. Why LA7..LA5 are not connected directly to the NOR but controlled? what these signals mean?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello again, why Data bus has not opposite numbering too? I mean, you use LAD0 as the less significant. Why? And where is all this information about the microprocessor, I can not find any help at the data sheet. My company has an NDA with NXP, so I guess that I could be able to access to any necessary information.

Best regards,

Paula.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the processor point of view, every address value addresses one byte. When you connect 16 bit memory device to the processor, each 16-bit memory cell in the memory is actually 2 bytes. To address 16-bit memory device connected to processor, LA31 is not used, because this address line is used to distinguis between individual bytes in one 16-bit word, which is not necessary if your memory device has 16-bit wide data bus and may read all 16-bit per one bus transaction. Therefore, LA31 is not used for connection in 16-bit mode. Similarly, for 32-bit device two least significant address bits should not be used for connection.

By "16-bit" and "32-bit" I mean data port size of the memory device connected.

For the information about functional description of the P5040 processor please look P5040 Reference Manual. This document is available for download from P5040 product page, "Documentation" tab:

On P5040Ds board upper address lines LA7..LA5 are used to create "virtual banks", to do that these lines are connected through XOR gates controlled by CPLD. This is to have a possibility to invert upper 3 address lines if necessary.

Yes, data bus numbering is also opposite - LAD0 is most significant data bit. Also, data lanes should be connected as described in P5040 Reference Manual, Table 13-2:

LAD[0:31]

Multiplexed address/data bus. For configuration of a port size in BRn[PS] as 32 bits, all of LAD[0:31]

must be connected to the external RAM data bus, with LAD[0:7] occupying the most significant byte lane

(at address offset 0). For a port size of 16 bits, LAD[0:7] connect to the most-significant byte lane (at

address offset 0), while LAD[8:15] connect to the least-significant byte lane (at address offset 1);

LAD[16:31] are unused for 16-bit port sizes. For a port size of 8 bits, only LAD[0:7] are connected to the

external RAM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alexander, thank you very much for your answer.

I need some extra help.

If LA31 is the LBS bit, for less than 32 address lines I should ignore the extra eLBC address most significant lines (LA00, LA01...).

I don't understand what you mean that for 16-bit port size LA31 is don't care, why?

A 16-bit port means that you have 16 address lines, right?

And, why for a 25 address lines LA31 is also don't need. I don't understand this logic.

Thank you in advance.

Best regards,

Paula.