- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- SPI for S12ZVC

SPI for S12ZVC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am new user using S12ZVCA. I already make a board(refer DEVKIT-S12ZVC). And it work fine.

I am excised GPIO(DEVKIT-S12ZVC_LAB1GPIO.zip) and it work fine.

But, I have issue on SPI(DEVKIT-S12ZVC_LAB5SPI.zip). I don't know how to use Processor Expert.

My 1st project need using ADC(HVI) to measure 0~10V. And transmit data using SPI. And control some GPIO.

Do you have other SPI example without Processor Expert? What is best way for my 1st project?

Best Regards,

Aaron

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

I have tested the SPI on a simple example code and the behavior you describe is correct.

I have the same results and I can read the data on pins.

The SPI0DRL register is not a regular register.

When you write to it, you write to TX register and it is immediately transmitted to shift register.

The 0x00FF is probably a mask, it means you have configured 8-bit transfer width.

In case SPI0CR2_XFRW == 1 (16-bit transfer width), the mask is then 0xFFFF.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

We don’t have SPI example for S12ZVC yet, but S12XEP has the same S12SPIV5 module, so you can refer to the attached example. You have to reroute the SPI you are going to use to a Port (MODDR).

ProfessorExpertHelp.pdf is in the root folder of CodeWarrior, if you need help with that.

Regarding ADC(HVI), an external resistor R_EXT_HVI (10k) must be connected to the HVI (see Figure 2-35). Disable digital input (DIENL) and enable ADC connection (PTAENL), select divider (PIRL) with ratio 2 or 6 (see Table G-1), so that your input voltage will be in range of Vssa; Vrh. And set up ADC to measure internal channels 5/6.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can not write new value to SPI0DR. The register of SPI0DR is always 0x00ff. Why?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have noticed that SPIF (SPI0SR) flag is set, it means received data has been transferred into SPI0DR. Therefore, try clearing that flag, please refer to Table 15-8.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

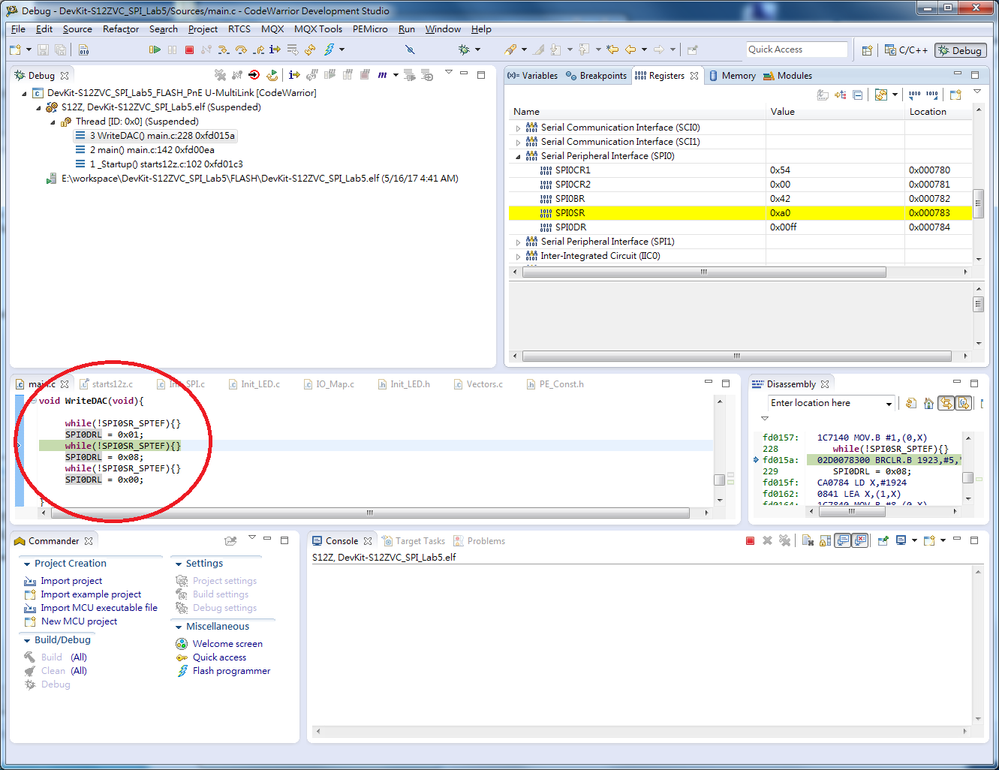

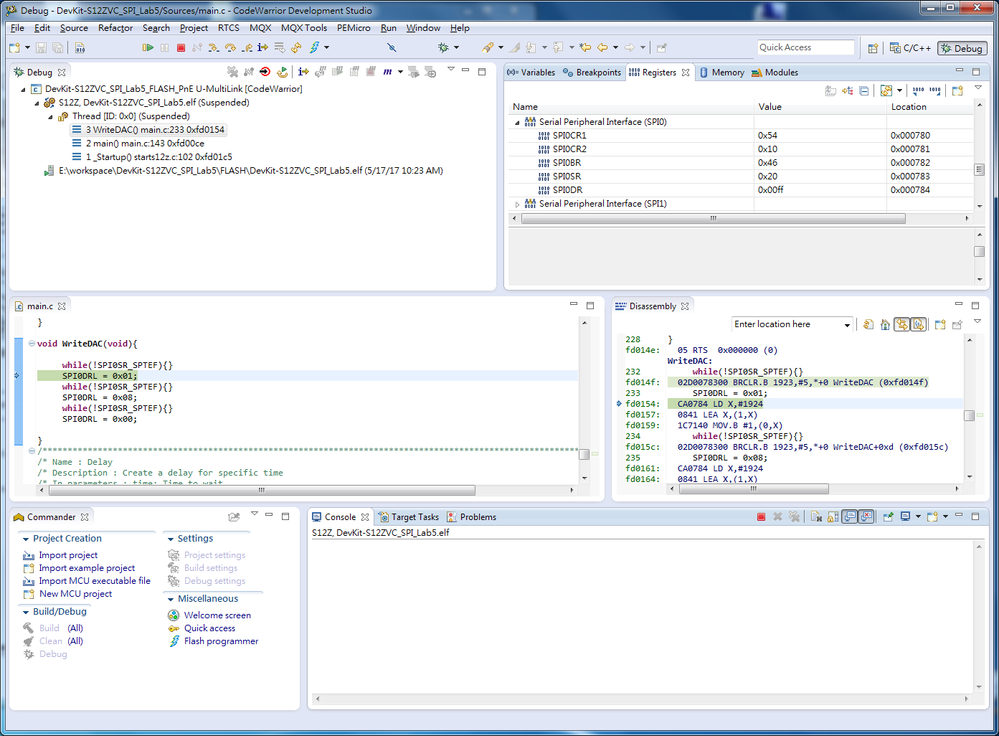

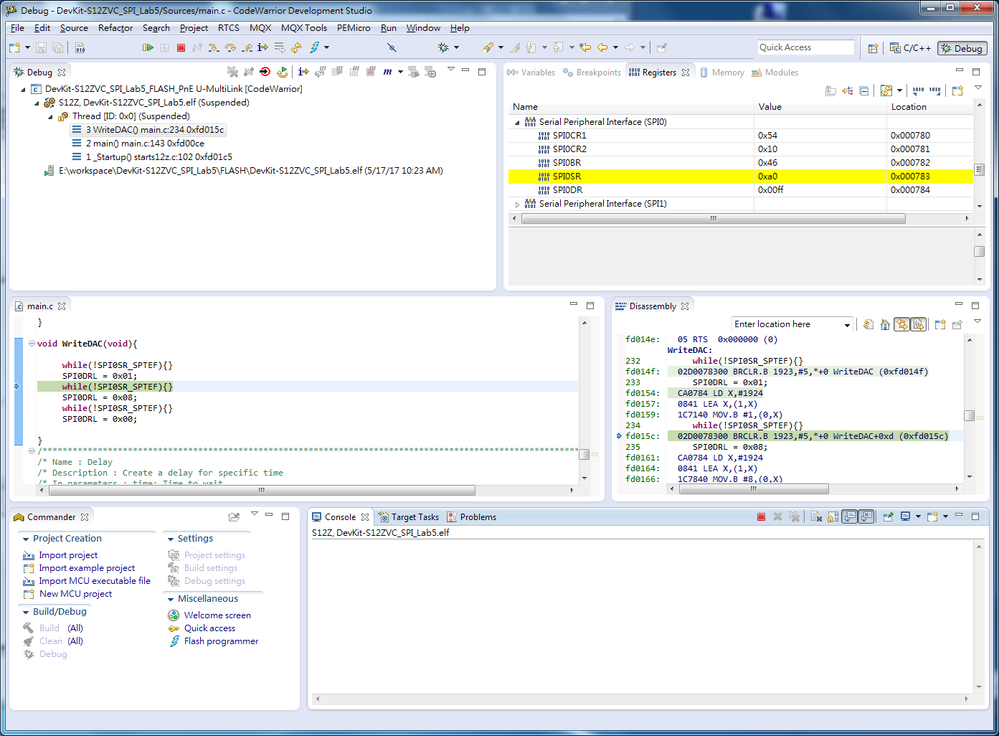

The SPIF (SPI0SR) flag is clear before write 0x01 into SPI0DR.

execute next step, the SPI0SR change to 0xa0.

It mean the SPIF (SPI0SR) flag is set after write 0x01 into SPI0DR.

but I can not see the SPI0DR=0x01. Why?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

I have tested the SPI on a simple example code and the behavior you describe is correct.

I have the same results and I can read the data on pins.

The SPI0DRL register is not a regular register.

When you write to it, you write to TX register and it is immediately transmitted to shift register.

The 0x00FF is probably a mask, it means you have configured 8-bit transfer width.

In case SPI0CR2_XFRW == 1 (16-bit transfer width), the mask is then 0xFFFF.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Daniel,

Now it can working. Thank you.

I record something in SPI example code for DEVKIT-S12ZVC

Best Regard,

Aaron