- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX6SDL CSI2IPU gasket non-gated clock issue

i.MX6SDL CSI2IPU gasket non-gated clock issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX6SDL CSI2IPU gasket non-gated clock issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have a FPGA mipi camera which works well with the non-continuous clock mode. The clock stays in LP11 when idle. The registers that makes the camera working including

- CSI2IPU_SW_RST..CLK_SEL = 0 (gated mode)

- IPU_CSI0_SENS_CONF.CSI0_SENS_PRTCL = 000 (gated clock mode)

Modified FPGA and set to continuous clock mode, the camera stopped working. In continuous clock mode, the clock is always the HighSpeed clock.

We tried the following changes to the drivers, but no luck:

- CSI2IPU_SW_RST.CLK_SEL = 1 (non-gated mode)

- IPU_CSI0_SENS_CONF.CSI0_SENS_PRTCL = 001 (non-gated clock mode)

The IPU_INT_STAT_1 shows that there was no IPU DMA interrupts generated. It seems that the gaskit didn't capture either the V-SYNC signal or a frame.

Does anyone work out a mipi camera on imx6sdl using continuous clock, which has no low-power state? What changes on the registers need to be done?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jasper

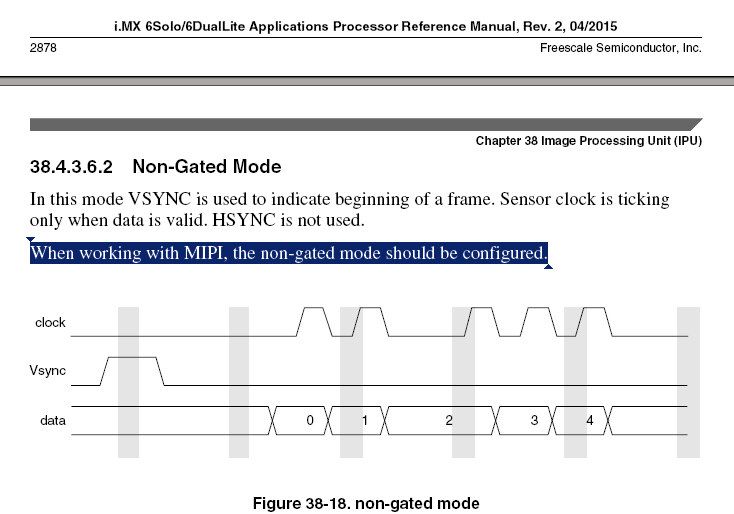

according to i.MX6SDL Reference Manual IPU hardware supports only below mode

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, Igor.

I checked the ov5640 mipi camera on SabreSD board. OV5640 0x4800.bit5 controls clock lane mode.

- CSI2IPU_SW_RST.CLK_SEL must be set to 0 (gated clock mode).

- IPU_CSI0_SENS_CONF.CSI0_SENS_PRTCL can be 0 (gated) or 1 (non-gated)

It's interesting that the clock mode of PHY register CSI2IPU_SW_RST must be set to gated mode no matter the clock is gated or free running.

There are two type of mipi clocks inside i.MX6:

- PHY input clock, from camera

- CSI2 output clock, the pixel clock to CSIx

I believe 38.4.3.6.2 talks about CSI2 output clock, which is controlled by IPU_CSI0_SENS_CONF.CSI0_SENS_PRTCL.

Does anybody know what CSI2IPU_SW_RST.CLK_SEL=1(non-gated) is supposed to use for?