- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Obtaining advertised ECSPI timing on SS_B

Obtaining advertised ECSPI timing on SS_B

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm using the i.MX7d with the linux 4.1.15 2.0.0 GA kernel, with a SPI peripheral connected to ECSPI3. This is on the MX7D sabre board. I need to have precise timing on the ECSPI transactions, and having read the reference manual and the datasheet it seems that it should be able to meet my needs. However, I'm seeing unexpected results.

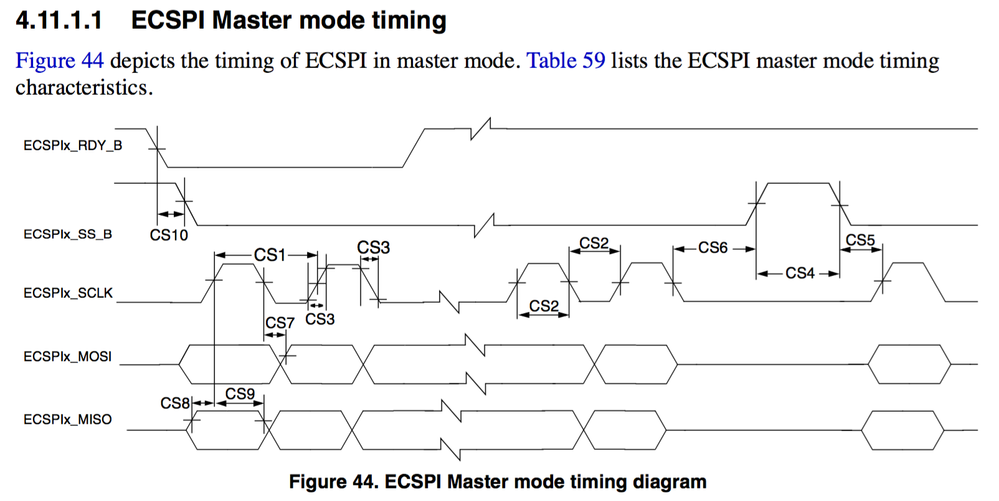

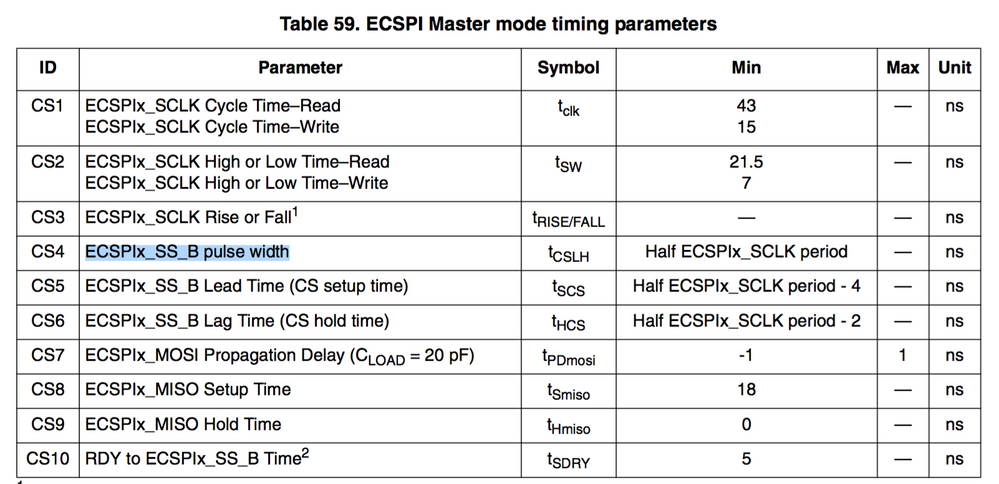

I need transactions (SS assertions) to occur at 1 MHz, and the SCLK to run at 16 MHz. Burst width is set to 14 bits. From the timing diagram in section 4.11.1.1 of the IMX7DCEC Electrical Characteristics document:

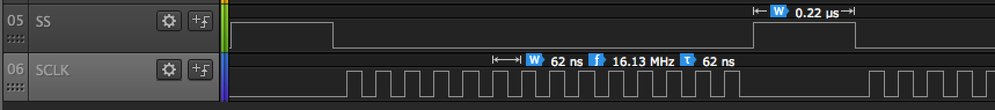

Given a SCLK at 16MHz, I would expect the CS4 time to be half a SCLK period as advertised, so CS4 should be approximately 32ns. However, I see a much larger CS4 time: about 220ns:

What could be causing this discrepancy? I am not using the PERIODREG register:

# devmem 0x3084001C 0x00000000

I set the ECSPI ipg and per clocks to 48 MHz:

# cat /sys/kernel/debug/clk/clk_summary | grep ecspi3 ecspi3_src 1 1 240000000 0 0 ecspi3_cg 1 1 240000000 0 0 ecspi3_pre_div 1 1 240000000 0 0 ecspi3_post_div 1 1 48000000 0 0 ecspi3_root_clk 2 2 48000000 0 0

Relevant ECSPI3 registers:

CONREG: 0x00D020F5

CONFIGREG: 0x00000100

How can I achieve the advertised timing on the SS_B pulse width?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonah

IC team confirmed that CS4 need 3.5 clk cycle after checking the RTL code , which conforms to the data from customer.

----------------------------

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jonah,

- Can the CS hold time be lowered to the published timing?ANSWER. Yes, we warranty that number publish

- If not, will the CS hold time at least be guaranteed to be consistent, given that the TXFIFO is always kept filled? ANSWER. The value that you see, I don´t see any problem to warranty that it is going to be consistent

Saludos,

Jaime

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jamie,

Thanks for the reply!

Can the CS hold time be lowered to the published timing?ANSWER. Yes, we warranty that number publish

Ok. I would like to lower the CS time to the published number. Can you explain how?

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jonah,

This is going to take further time, since we need to escalate the issue to our Apps team, so they can provide the steps to test it exactly to obtain this number, I do not have an exactly time since it is based on the load of the team. Hope you understand.

igorpadykov, can you please open an internal thread, so the apps team help us, to obtain the steps to reproduced the exact number of the datasheet.?

Best Regards,

Jaime

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jamie,

Thanks again for looking into this. My team is asking for an update. Do you have any news to share at this point?

Best,

Jonah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonah

I sent to case # 00110978 full copy of internal thread

with latest update.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello igorpadykov jamesbone,

I need an answer on this. We need to make a call ASAP on a BOM change due to this issue. It's been a month since I raised this, and I don't think it's unreasonable to expect some sort of reply by this point.

Please get me your final answer on this issue by Thursday AM at the latest.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonah

I sent this on internal thread

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, igorpadykov!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonah

IC team confirmed that CS4 need 3.5 clk cycle after checking the RTL code , which conforms to the data from customer.

----------------------------

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the update. Not great news, but at least we know what we're dealing with. It would be good to issue some sort of update to the timing specification to reflect this fact.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jonah,

Our Apps team it is doing some research, as soon as we get an update, Igor, would provide the update. I apologize for the latency response.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, Jamie. I look forward to hearing the results of your investigation.

Jonah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonah

for internal thread it is necessary to provide personal data info:

company name and customer e-mail. Could you provide it (one can provide it using service request)

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Igor,

I have filed case # 00110978 with this information.

Jonah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonah

From the RM I got the folllowing:

"The SPI_RDY enables fast data communication with fewer software interrupts. By

programming the ECSPI_PERIODREG register accordingly, the ECSPI can be used for a

fixed data transfer rate."

SPI_READY is enabled by DRCTL (bits 17–16 of CONREG), which seem to be at 00 (SPI_RDY ignored) on your register 0x00D020F5

The SPI_READY reference is under 10.1.4.4.1 Typical Master Mode.

Let me know if this helps!

--------------------------------

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for the reply. I am very familiar with this signal, as I use it in some of my other SPI peripherals. However, I do not have a SPI_RDY signal from this specific SPI peripheral. (Some SPI slaves emit this signal, but some do not.)

So, you are saying that I can achieve the advertised timing with a SPI_RDY signal?

Jonah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonah

datasheet CS4 time to be half a SCLK period depicts as "min". time,

it may be bigger depending on internal latencies caused, for example

linux. One can try with baremetal test to achieve better timings.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, I notice that this SS hold time is exactly the same (within 2 ns) on every single transaction, for millions of transactions in a row. This makes me worried that this SS hold is a hardware limitation of some kind. If so, I really need to know ASAP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonah

for example time necessary for moving by A7 core next portion of data from ddr to ecspi fifo

might cause "internal latencies".

Best regards

igor