- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- No output from SPI

No output from SPI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

No output from SPI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using Kinetis K10 device with CodeWarrior with Processor Expert. The Processor expert code isn't producing an output on the SPI. So I'm trying to manually get it to work. My init and write functions are below, and via the register view in CodeWarrior I can see all the correct data is being written to the registers, but when I look at the SPI lines on a scope, they're doing nothing (i.e. CLK isn't even moving!)

The exact part I'm using is MK10DX32VLF5, I'm running in SPI master mode my SPI lines are:

- Port D 0 - SPI0_PCS0 - Chip Select

- Port D 1 - SPI0_SCK - SPI Clock

- Port D 2 - SPI0_SOUT - Data Out

- Port D 3 - SPI0_SIN - Data In (Not used and currently not connected)

As there's not output at all - I can't work out what I've missed out (I'm assuming it's something I've done wrong or omitted).

void main(void)

{

SPI_Init();

while (1)

{

delay_ms(500);

SPI_Write16(0xBE);

}

}

void SPI_Init(void)

{

PORTD_PCR0 = PORT_PCR_MUX(2); // Port D0 is SPI Chip Select

PORTD_PCR1 = PORT_PCR_MUX(2); // Port D1 is SPI Clock

PORTD_PCR2 = PORT_PCR_MUX(2); // Port D2 is SPI Data Out

PORTD_PCR3 = PORT_PCR_MUX(2); // Port D3 is SPI Data In

SIM_SCGC6 |= SIM_SCGC6_SPI0_MASK;

SPI0_MCR = SPI_MCR_MSTR_MASK |

SPI_MCR_DCONF(0x00) |

SPI_MCR_PCSIS(1) |

SPI_MCR_CLR_TXF_MASK |

SPI_MCR_CLR_RXF_MASK |

SPI_MCR_SMPL_PT(2) |

SPI_MCR_HALT_MASK;

SPI0_CTAR0 = SPI_CTAR_FMSZ(15) |

SPI_CTAR_PCSSCK(2) |

SPI_CTAR_PASC(2) |

SPI_CTAR_PDT(2) |

SPI_CTAR_PBR(2) |

SPI_CTAR_CSSCK(2) |

SPI_CTAR_ASC(2) |

SPI_CTAR_DT(2) |

SPI_CTAR_BR(2);

SPI0_SR = SPI_SR_TCF_MASK |

SPI_SR_EOQF_MASK |

SPI_SR_TFUF_MASK |

SPI_SR_TFFF_MASK |

SPI_SR_RFOF_MASK |

SPI_SR_RFDF_MASK |

SPI_SR_TXCTR(0x00) |

SPI_SR_TXNXTPTR(0x00) |

SPI_SR_RXCTR(0x00) |

SPI_SR_POPNXTPTR(0x00) |

0x00200000U;

}

uint8_t SPI_Write16(uint16_t data)

{

SPI0_SR = SPI_SR_TCF_MASK |

SPI_SR_EOQF_MASK |

SPI_SR_TFUF_MASK |

SPI_SR_TFFF_MASK |

SPI_SR_RFOF_MASK |

SPI_SR_RFDF_MASK |

SPI_SR_TXCTR(0x00) |

SPI_SR_TXNXTPTR(0x00) |

SPI_SR_RXCTR(0x00) |

SPI_SR_POPNXTPTR(0x00) |

0x00200000U;

SPI0_PUSHR = SPI_PUSHR_CTAS(0) |

SPI_PUSHR_EOQ_MASK |

SPI_PUSHR_CTCNT_MASK |

SPI_PUSHR_PCS(1 ) |

data;

// Start Transfer

SPI0_MCR &= ~(SPI_MCR_HALT_MASK);

#warning no check timeout set

while ( (SPI0_SR & SPI_MCR_HALT_MASK) == 0);

return (1);

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ben,

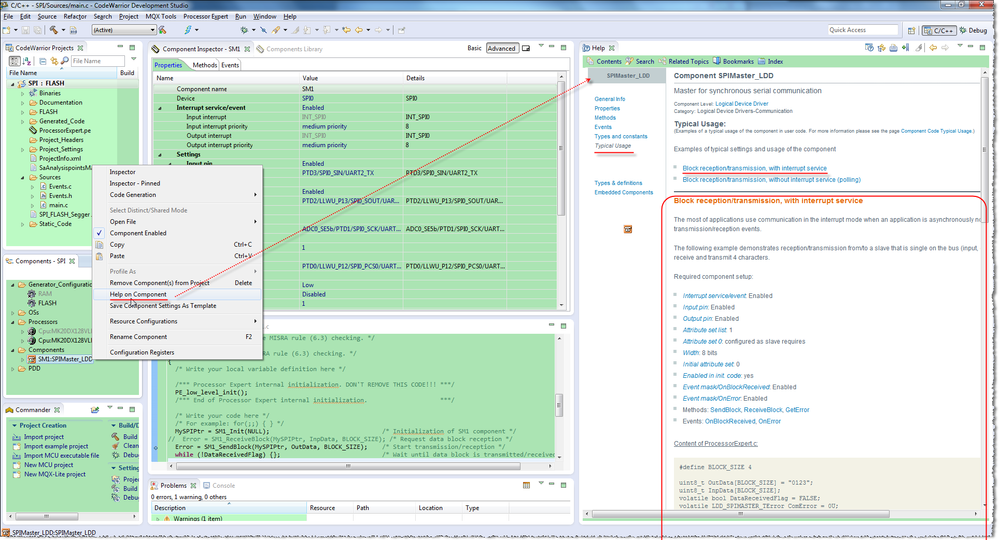

Have you try to test the Typical Usage "Block reception/transmission, with interrupt service " of SPIMaster_LDD.

Test it on FRDM-K20D50M board, I was able to observe the SPI waveform on oscilloscope.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------