- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- About Time Quanta and SSP offset

About Time Quanta and SSP offset

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

About Time Quanta and SSP offset

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

I have been developping CAN FD related item.

And I have to check Time Quanta and SSP(secondary sample point) offset.

So please someone helps me.

1. Time Quanta

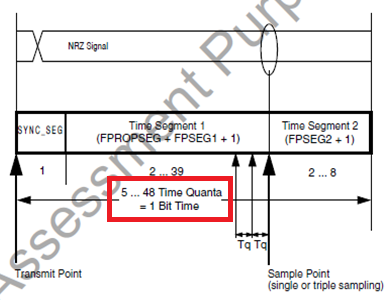

- at CAN FD frame, Time Quanta in Arbitration phase and Data phase are 5 ~ 48 TQ range. right?

<captured on page 1293>

2. How to check SSP offset value?

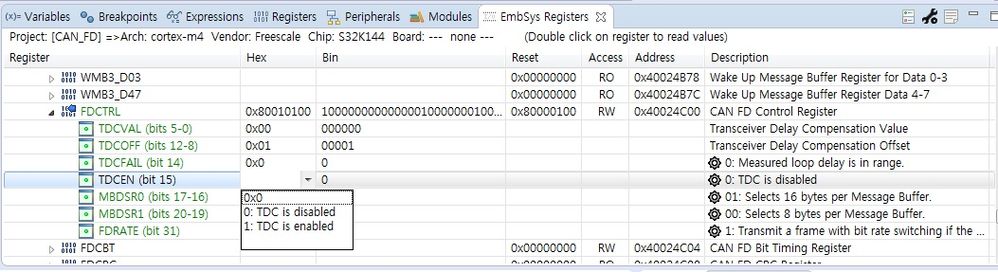

- at debuging window, there is not any value.

<captured on S32DS debuging window>

Thank you.

Kim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kim,

1.

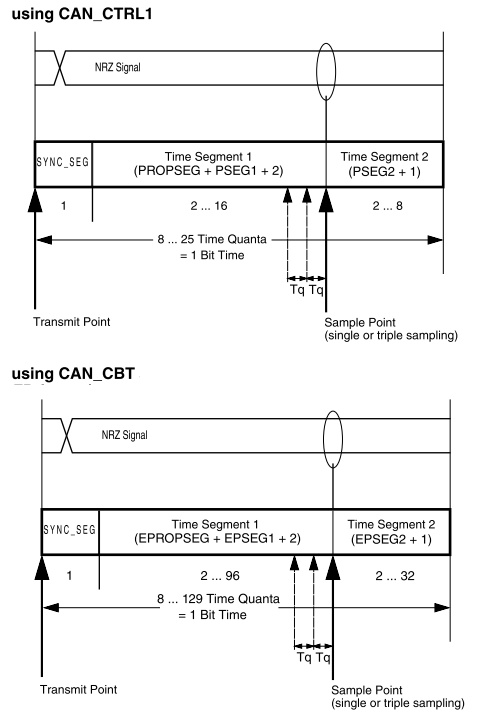

The bit time during an Arbitration phase is defined by CTRL1 or CBT register.

Note the CBT must be used when CAN FD feature is enabled.

Then the length of bit can have below time quantas.

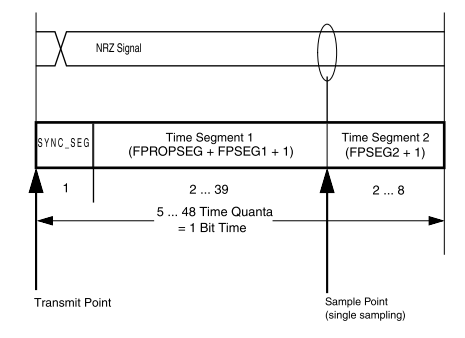

The bit time for the Data phase is defined by FDCBT register, as below, if the bit rate switching is enabled for CAN FD frame (FDCTRL[FDRATE]=1 and the BRS bit of the Tx MBs is set). Otherwise CTRL1 or CBT registers control bit time of Data phase.

2.

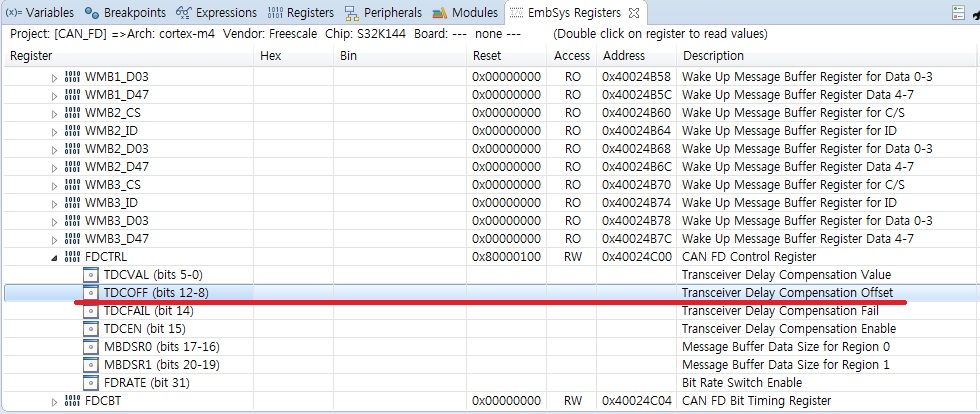

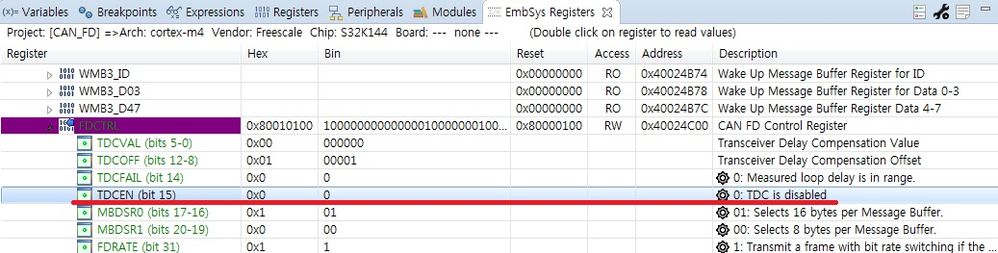

The position of the secondary sample point is defined by the measured loop delay time added to an offset value specified in CAN_FDCTRL[TDCOFF]. CAN_FDCTRL[TDCVAL] bit field stores the result of this calculation.

The TDC mechanism can be enabled by the CAN_FDCTRL[TDCEN] bit and is effectiveonly during the data phase of FD frames having the BRS bit set. It has no effect either on non-FD frames, or on FD frames transmitted at normal bit rate.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi. Petr.

Thank you for your answer.

For question 1, Time quanta, I understood as below.

- CAN FD arbitration phase : using CAN_CBT

- CAN FD data phase : using CAN_FDCBT

For question 2, How to check SSP offset value, I understood your explanation.

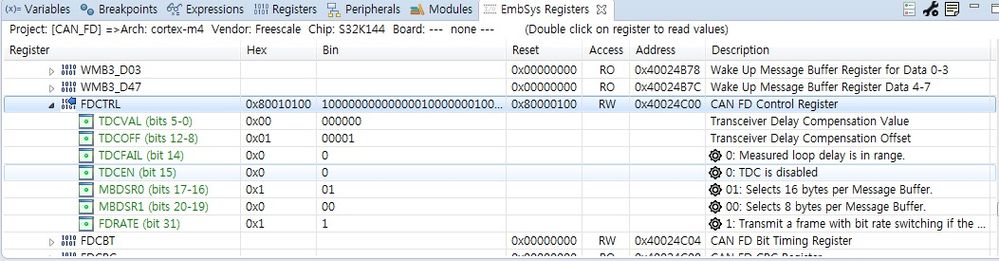

But I could not confirm that the bit of TDCEN and TDCOFF was changed.

- I changed the bit of TDCEN and TDCOFF at the EmbSys Registers but these bits were not changed.

- So I changed these bits at the source code, but I was not sure that these bits were changed.

Because these bits at the EmbSys Registers were changed(1) during RUN but were returned to initial value(0) during SUSPEND.

How can I change the bit of TDCEN and TDCOFF and confirm whether changed or not?

Should I think these bit as changed?

■ At the EmbSys Registers :

1. I changed TDCEN bit to 1

2. but this bit was not changed (the bit was returned to initial value 0, TDC is disabled)

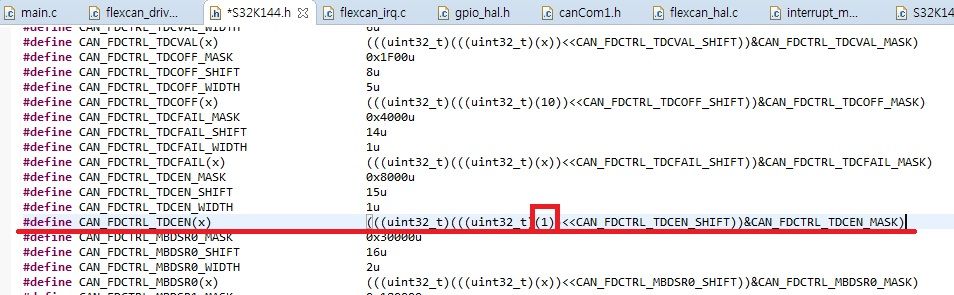

■ At the source code :

1. I changed TDCEN bit to 1

< Before code change >

< After code change : from x to 1 >

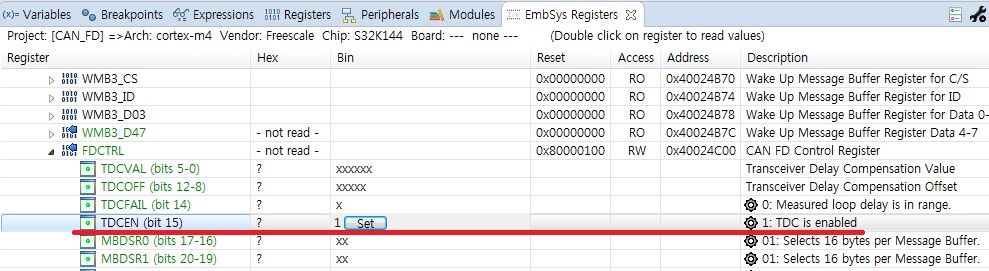

2. and TDCEN bit was changed (enabled) during RUN.

3. but TDCEN bit was returned to initial value (disabled) during SUSPEND

Thank you

Kim.