- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5748G startup.S

MPC5748G startup.S

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5748G startup.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,team :

I found the startup.S function that difference between the MPC5748G demos : flexcan_receive(...:\flexcan_receive\flexcan_receive_Z4_0\Project_Settings\Startup_Code),

linflexd_uart(...:\linflexd_uart\linflexd_uart_Z4_1\Project_Settings\Startup_Code).

Here the pictures are below:

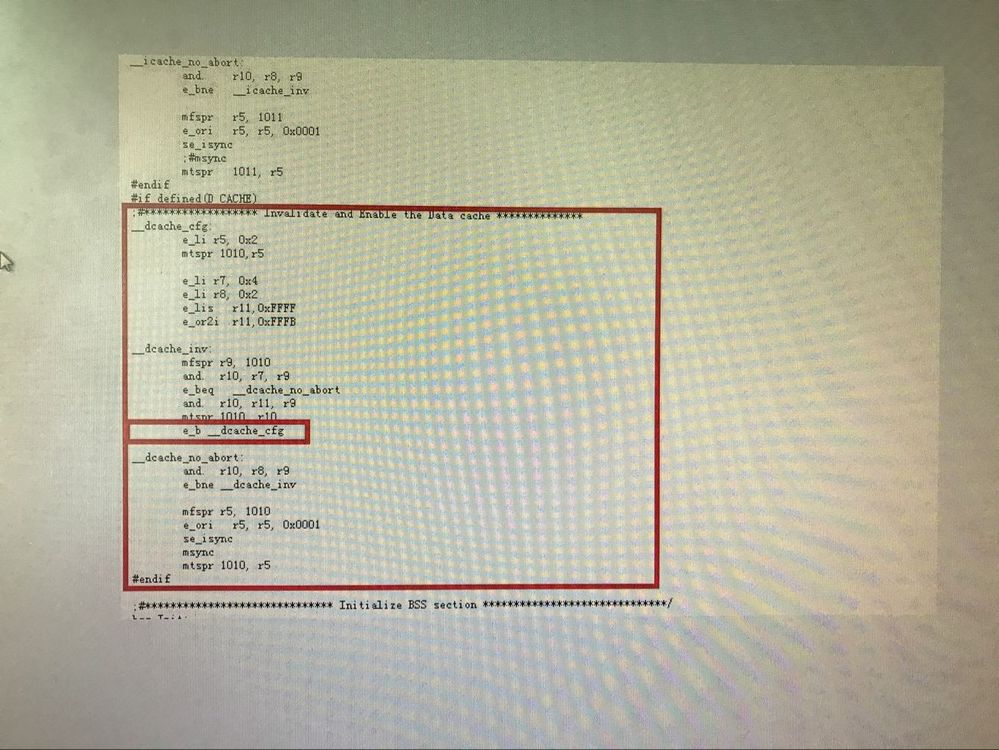

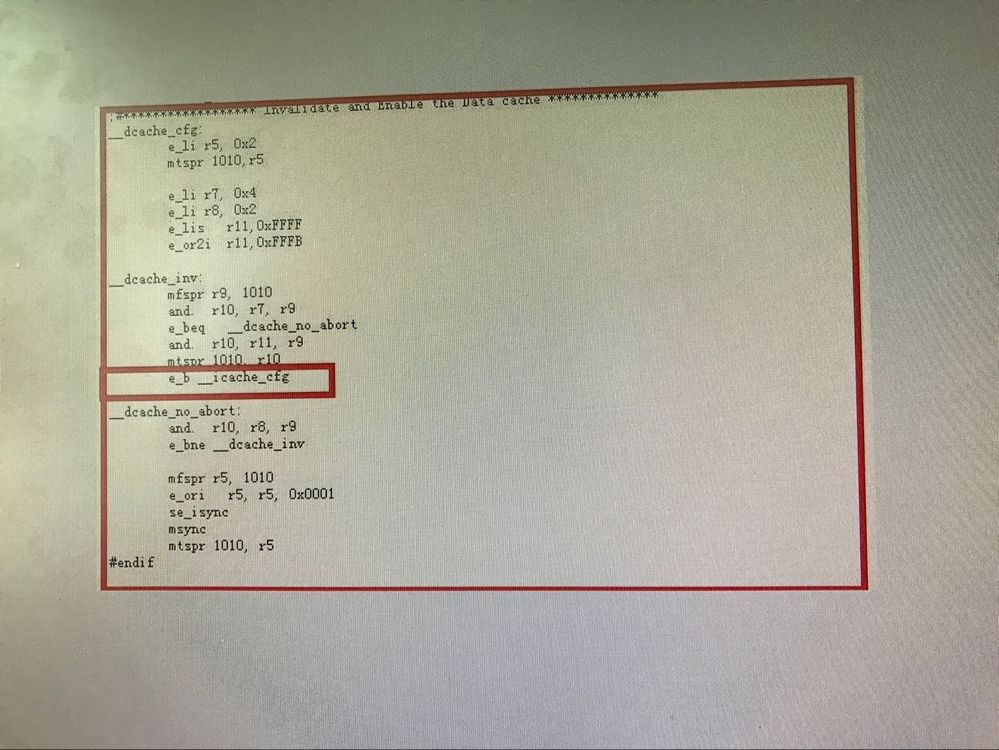

1.flexcan_receive : e_b __dcache_cfg in the __dcache_inv

2. linflexd_uart : e_b __icache_cfg in the __dcache_inv

Now I uesd flexcan_receive example in my project, and we needed to integrate uart(channel 2) receive module. linflexd_uart example can receive the correct char which we need, but in my project uart ch2 always received '0'. I contrasted these examples,and found there is differece betwwen them in Startup_Code. I copyed the

linflexd_uart\linflexd_uart_Z4_1\Project_Settings\Startup_Code \ startup.S to flexcan_receive\flexcan_receive_Z4_0\Project_Settings\Startup_Code\ startup.S .At last uart ch2 can receive the correct char which we need.

Why?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I tested linflexd_uart example with both startup source files and it works correct. But the second startup ( 2. linflexd_uart : e_b __icache_cfg in the __dcache_inv) is definitely incorrect.

S32 Design Studio version 1.1 has startup fix and correct cache initialization is the first one (1.flexcan_receive : e_b __dcache_cfg in the __dcache_inv).

Could you please try to disabled cache in your project to eliminate startup difference to UART functionality?

Do you use DMA in your project?

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

That's funny. My projrct uses the second startup that works well, and the first startup doesn't work well for uart mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

it is very strange behavior, because the typo in cache configuration should not have any influence to UART (if you do not use DMA).

Is this the only difference in your projects?

Could you please send me two simple projects (the working one and the second which does not work) which demonstrates the issue? I would like to test it on my side.

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please wait a few days for me.