- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Flex BUS interface issue.( MK66 )

Flex BUS interface issue.( MK66 )

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Flex BUS interface issue.( MK66 )

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai .,

I am working with MK66FN2M0VLQ18 MCU in our customized board. I am using sdk2.0 examples for flexbus initialization.

I have configured the flexbus as 2 bytes data width , 8 WS, burst read/write disabled mode. since i am interfacing slow device I disable the auto acknowledgement (AA) and considering the RDY signal from external device.

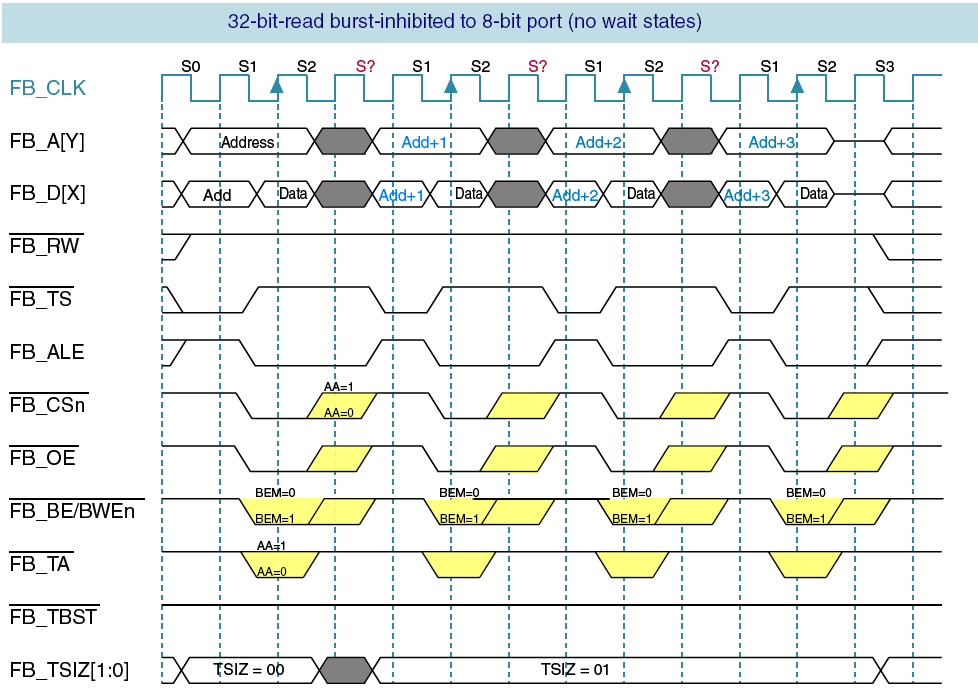

In burst inhibited mode if I write 32 bit data to 16 bit port size, it will generate two CS pulses and each cycle has to wait for external RDY signal to close the cycle, as mentioned in reference manual.

But in our case on getting first RDY signal , the complete bus transaction getting close irrespective of waiting for second RDY signal(hence i am getting single CS pulse despite of writing data size more then port width) .

I tried the same configuration by neglecting external RDY signal(FB_TA), in that time I am getting two CS pulse .

/**********************flex bus config routine **************************/

flexbus_config_t flexbusConfig;

FLEXBUS_GetDefaultConfig(&flexbusConfig);

flexbusConfig.waitStates = 0x0FU;

flexbusConfig.chipBaseAddress = 0x60000000U;

flexbusConfig.chipBaseAddressMask = 0x7FU;

flexbusConfig.portSize = kFLEXBUS_2Bytes;

FLEXBUS_Init(FB, &flexbusConfig);

/****************************************************************************/

Please suggest me If committed to any mistake while configuration.

Thank you.,

Best Regards.,

Karthik

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Karthik,

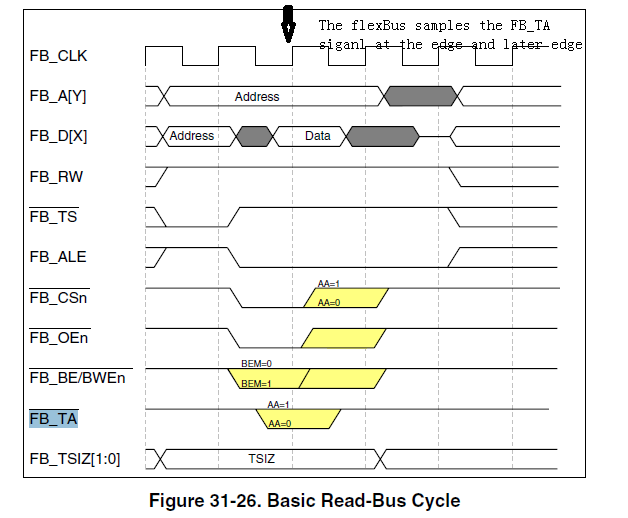

I see that you use CPLD or FPGA to generate the FB_TA signal, as I have said that you have to do a state machine, the falling edge of CSx can trigger the state machine, you have to use FB_CLK to do the state change of the state machine. You can not generate the FB_TA without FB_CLK involved.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, xiangjun.rong,

Thank you for your response.

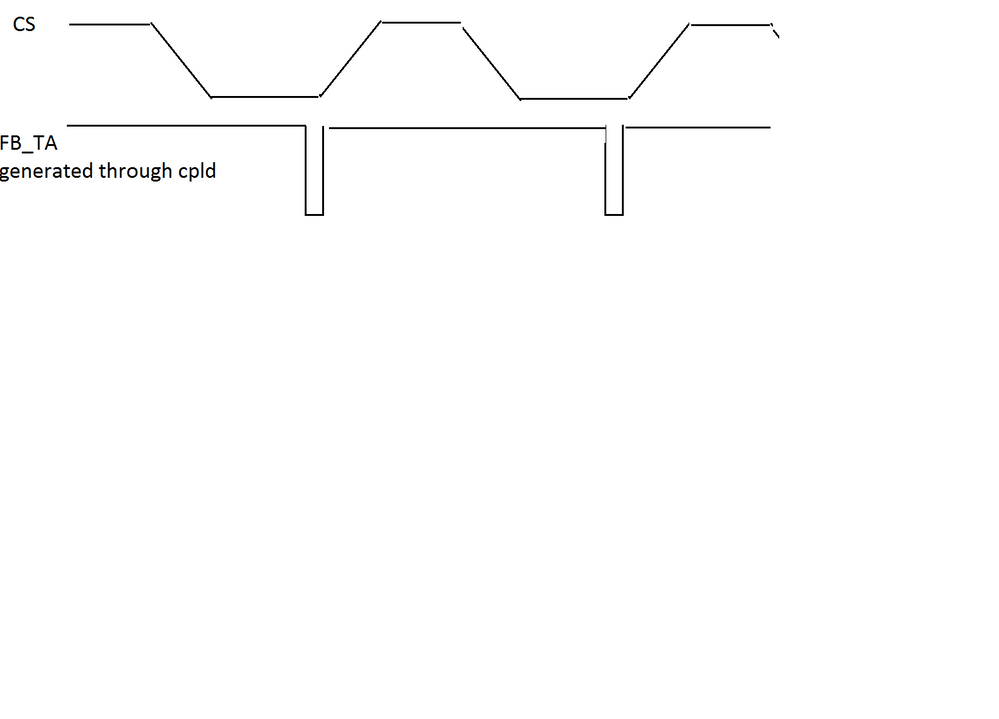

Yes I am using CPLD to generate FB_TA signal. The waveform exactly look like below , Upon getting first ready signal whole bus transfer getting closed, hence the second CS pulse is not generating. these signals I analyzed by keeping into Auto ACK mode and neglecting the RDY signal(i,e I changed the FB_TA pin mux option to another ).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Karthik,

I do not know how you generate the FB_TA signal without the FB_CLK signal involved, for example, how to control the delay from falling edge of /CS to the falling edge of FB_TA signal. Anyway, you should assert the FB-TA signal from the risng edge of FB_CLK as the following figure. you can refer to the Altera or whatever for the VHDL code.

BR

XiangJun Rong