- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- [SOLVED] Possible problem with EMC/static memory access LPC54608

[SOLVED] Possible problem with EMC/static memory access LPC54608

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[SOLVED] Possible problem with EMC/static memory access LPC54608

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have my first (test) board with the LPC54608 on my desk now. The board includes 8 MByte of SDRAM (x16 bit) and a NAND Flash (x8 bit) among other things.

The SDRAM works as it should, it passes various test patterns etc so I know that the interface for that one is working.

I also have a ST NAND256 Flash device mounted.

The EMC-WE (P0.15) signal is connected both to the SDRAM (WE#) and the NAND Flash (WE#).

The EMC-CSN0 (P0.16) signal is connected to the NAND Flash as chip select.

(EMC-OE (P0.17), EMC-A18 (P3.29), EMC-A19 (P3.30) are connected to NAND Flash (R#, AL, CL))

The problem I see is that if I configure the Static memory controller 0 (CS0) and makes read access to address 0x80000000 and upwards, I see activity on the EMC-CSN0 and EMC-OE as expected. However, if I do write requests to the same area, I only see the EMC-CSN0 toggling and no activity on the EMC-WE pin.

(and remember, the SDRAM works fine, EMC-WE toggles nicely when accessing SDRAM)

Is there something specific I need to be aware of when dealing with static memory on the EMC bus of the LPC54608 especially with regards to the EMC-WE signal ?

The clock is set to 180 MHz

The init code for the static memory (I know, not pretty at the moment :smileywink:)

(Contents of the registers of the EMC static memory controller verified with Keil debugger)

Chip_Clock_EnablePeriphClock(SYSCON_CLOCK_EMC);

/* Init EMC Controller -Enable-LE mode */

Chip_EMC_Init(LPC_EMC, 1, 0, 0);

Chip_Clock_SetEMCDiv(5);

/* Init EMC Dynamic Controller */

// Chip_EMC_Dynamic_Init(LPC_EMC, &IS42S16400_config, Chip_Clock_GetEMCRate());

LPC_EMC_T *EMC_Reg_add = (LPC_EMC_T *) ((uint32_t) LPC_EMC + ((0) << 5));

EMC_Reg_add->STATICCONFIG0 = 0;

EMC_Reg_add->STATICWAITWEN0 = 2;

EMC_Reg_add->STATICWAITOEN0 = 2;

EMC_Reg_add->STATICWAITRD0 = 8;

EMC_Reg_add->STATICWAITPAG0 = 0x1F;

EMC_Reg_add->STATICWAITWR0 = 8;

EMC_Reg_add->STATICWAITTURN0 = 0x0f;

LPC_SYSCON->EMCSYSCTRL= (1<<0) | (1<<2);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK,

found out what the problems was! The write signal for static memory is NOT the EMC_WE but rather the EMC_BLSN0..3 signals. When connecting the EMC_BLSN0 to the NAND Flash WE# pin it works.

I'm not sure it is exactly clear in the UM/DS what to use, Fig 116 on page 599 shows the "WE" signal going to the 8 bit memory device (and not BLSN0).

That coupled with the wording in Table 552 on page 574 confused me.

(also the fact that on the LPC177x the same schematics are shown in the UM on Fig 19. on page 206. Here WE is shown as write signal for a 8 bit memory device and on the LPC177x this is EMC_WE which works fine for an 8 bit device (no need to use EMC_BLSN0 for that device)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carsten Groen,

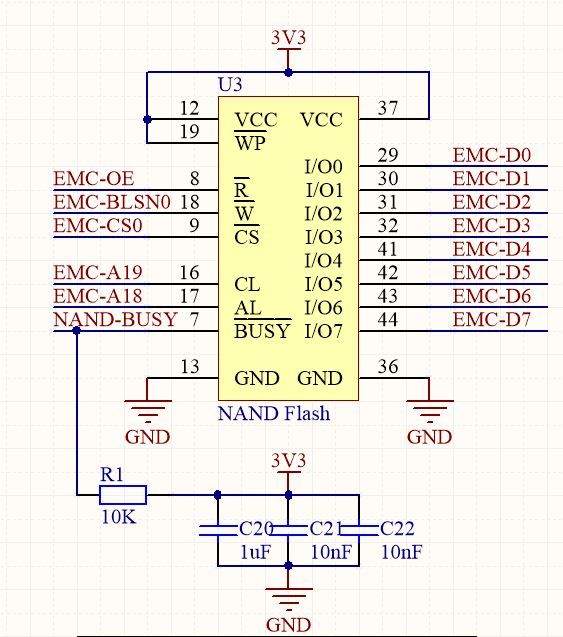

Thanks for your sharing, I was wondering if you can exemplify the sch of the conjunction of LPC54608 and NAND flash.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

I have attached the part of the schematic with the NAND Flash, hope it makes sense.

Connections on LPC54608 is:

EMC-D0..EMC-D7: P0_02 - P0_09

EMC-OE: P0_17

EMC-BLSN0: P1_17

EMC-CS0: P0_16

EMC-A19: P3_30

EMC-A18: P3_29

NAND Busy is just connected to a GPIO

Static memory space 0 is set as 8 bit interface.

This places the NAND Flash at the following addresses:

#define DATA (*(volatile unsigned char*)0x80000000) // Bit 18 and 19 = Low

#define ADDR (*(volatile unsigned char*)0x80040000) // Bit 18 = High

#define CMD (*(volatile unsigned char*)0x80080000) // Bit 19 = High