- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- S12ZVMB: P0, P1, E0, E1 usage as i/o

S12ZVMB: P0, P1, E0, E1 usage as i/o

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S12ZVMB: P0, P1, E0, E1 usage as i/o

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Refer to datasheet selection. Here can all 4 pins HS1, HS2 and PP0, PP1 be used independantly as IO. I have tried but not working. Am I missing any other setting for making all the four pins at independent IOs. I have similar issue with PE0 and PE1.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Can you try on the S12ZVMB EVM and check if ti is working with a very simple code.

Regards,

Rajiv.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rajiv,

I would like to but we don't have the S12ZVMB EVM board.

Regards

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Do you mean independent drivers and GPIO?

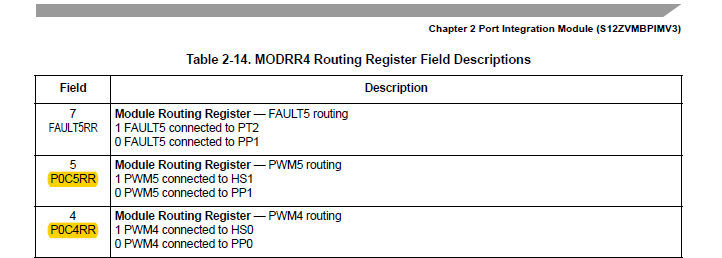

HS0-1 pins are set as independent drivers after reset (Tab 2-8), HSCR[HSEx] enable the drivers and HSDR[HSDRx] are used to control the drives. If PWM or TIM1 module is enabled and these pins are routed to the module in MODRR4 or MODRR5, the module takes control over these pins. That applies in general for all modules and associated pins (Table 2-45).

Note, registers MODRR4 and MODRR5 can be written only once in normal mode.

Port E and P are set as GPIO after reset (tab 2-3, 2-6). However, if external oscillator is enabled CPMUOSC [OSCE] the PE0 and PE1 pins are exclusively reserved for the oscillator and they cannot be used anymore as GPIO.

Regards

Daniel