- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- MM912J637 D2DFCLK and PRESC register

MM912J637 D2DFCLK and PRESC register

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MM912J637 D2DFCLK and PRESC register

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

We are using the MM912J637. Have been for a few years now but I think we are uncovering an old issue now.

I am finding the lifetime counter is giving a wake-up about 5% too early. I want 5 seconds but am seeing about 4.75 seconds. The error should be better than this as the system has been running and so the ALFCLK should have a recent sync against D2DSCLK. D2DSCLK should have an accuracy better than ~1%. (I'll ask another question on this though.)

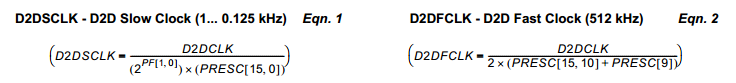

In working through this I am looking at the datasheet for the D2DFCLK and D2DSCLK settings. The description for the use of PRESC is:

Q1: Is the denominator for D2DFCLK really "2x(PRESC[15,10]+PRESC[9])"? So are there really two ways to get a denominator of 22, say; one with PRESC[15,10]=11 and PRESC[9]=0, and the other with PRESC[15,10]=10 and PRESC[9]=1? This seems a rather unusual implementation? Is the final parenthesis in the correct location?

Q2: As written, Eqn. 2 can't have an odd denominator. Is this really the case?

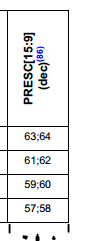

Further down in the datasheet (in section 4.3.5.3 of version V5.0 Jan 2015 of the datasheet), Table 69 has Recommended Clock Settings. The right-most column looks like:

Q3: What is the "63:64" content showing? Why the semi-colon?

(Also note that the register here is shown as PRESC[15:9] - using a colon rather than a comma as before (minor issue) but now showing bits 15 down to 9 - so a bit inconsistent.)

Many thanks for any assistance anyone can give.

Regards,

Ian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ian,

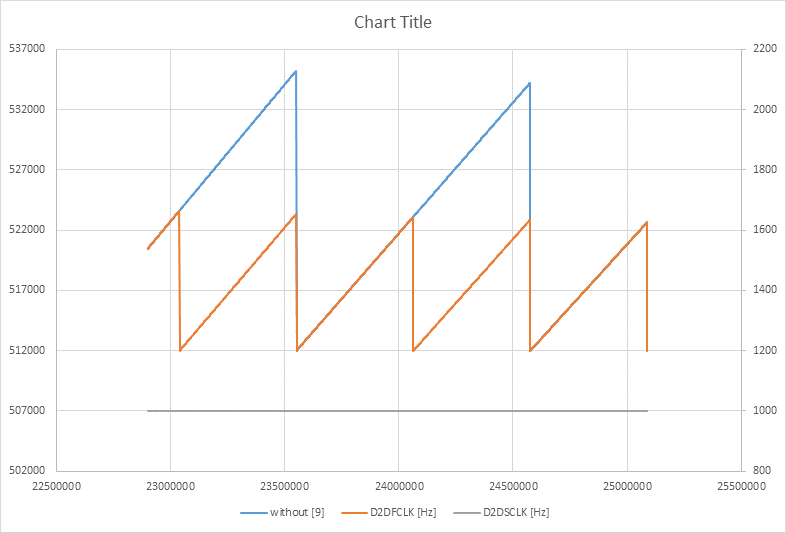

Q1. The equation is correct and there are two ways to get to e.g. 22. The reason is to be more flexible in the selection of clock sources (D2DCLK) and still select D2DSCLK / D2DFCLK to fit 1ms / ~512 kHz. See picture below with the + bit[9] reduces the blue line to the orange on.

Q3. This just reflects that there the two options to reach the same denominator.

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've fixed the initial problem I had - that is the LTC timeout being inaccurate - that was due to a configuration mistake in the PRESC register. I still think the documentation is a little unclear here though.

How is PRESC[9] handled for the D2DFCLK and why are there two numbers in the last column of Table 69.

Thanks,

Ian