- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- How to use freescale k64f flexbus ?

How to use freescale k64f flexbus ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to use freescale k64f flexbus ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Now I want to use flexbus to config the fpga; i can't find design demo of flexbus;only the driver

flexbus_config_t flexbusConfig;

FLEXBUS_GetDefaultConfig(&flexbusConfig);

flexbusConfig.waitStates = 2U;

flexbusConfig.chipBaseAddress = 0x60000000U;

flexbusConfig.chipBaseAddressMask = 7U;

FLEXBUS_Init(FB, &flexbusConfig);

I use the demo config the flexbus;but i can't measure

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, ZhaiLing,

As you said that we have not the example code for FlexBus. The FlexBus configuration is only dependent on your hardware connection, for example, the port size, wait state, byte-lane shift, multiplexed or non-multiplexed mode...

Anyway, the flexbusConfig structure corresponds to the FlexBus register contents, pls refer to the Chapter 31

External Bus Interface (FlexBus) in RM of K64, especially register setting.

After the FlexBus register setting, you can use a pointer to access the external memory, which locates in the FlexBus memory space, pls refer to Chapter 4 Memory Map.

If you still have question, pls tell us the hardware connection so that we can determine the flexbus register setting.

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,xiangjun.rong

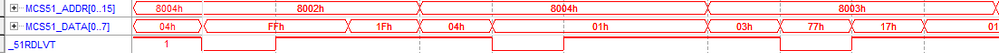

I read the date from the fpga;the flexbus address is 0x8003,the date is 0x77.

But i read the date is 0x17.I don't kown why ? where is the 0x17 come from?

The _51RDLVT is FB_OE.

Thanks and best regards

zhai

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, ZhaiLing,

Does the timing is from logic analyzer or tools of FPGA, I think it is possible that the data become from 0x77 to 0x17, when the FB_OE becomes high, which means that the FPGA do not drive the data bus, in other words, the data bus is float when the FB_OE becomes high.

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjun.rong

Yes,I grab the signal with the signaltap ii; The date of fpga send is always 0x77;when the FB_OE becomes high ,the date shoud be 0x77;

my configrations

void FLEXBUS_GetDefaultConfig(flexbus_config_t *config)

{

config->chip = 0; /* Chip 0 FlexBus for validation */

config->writeProtect = 0; /* Write accesses are allowed */

config->burstWrite = 0; /* Burst-Write disable */

config->burstRead = 0; /* Burst-Read disable */

config->byteEnableMode = 0; /* Byte-Enable mode is asserted for data write only */

config->autoAcknowledge = true; /* Auto-Acknowledge enable */

config->extendTransferAddress = 0; /* Extend transfer start/extend address latch disable */

config->secondaryWaitStates = 0; /* Secondary wait state disable */

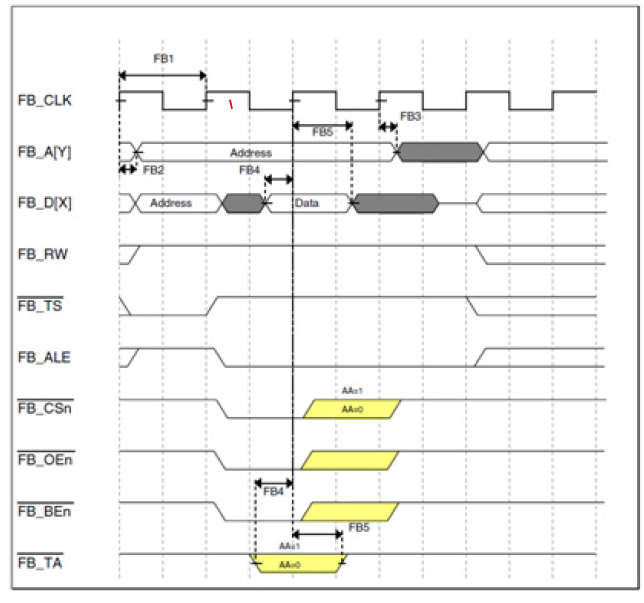

config->byteLaneShift =kFLEXBUS_Shifted;//kFLEXBUS_NotShifted; /* Byte-Lane shift disable */

config->writeAddressHold = kFLEXBUS_Hold1Cycle; /* Write address hold 1 cycles */

config->readAddressHold = kFLEXBUS_Hold2Or1Cycles; /* Read address hold 0 cycles */

config->addressSetup =

kFLEXBUS_FirstRisingEdge; /* Assert ~FB_CSn on the first rising clock edge after the address is asserted */

config->portSize = kFLEXBUS_1Byte; /* 1 byte port size of transfer */

config->group1MultiplexControl = kFLEXBUS_MultiplexGroup1_FB_ALE; /* FB_ALE */

config->group2MultiplexControl = kFLEXBUS_MultiplexGroup2_FB_CS4; /* FB_CS4 */

config->group3MultiplexControl = kFLEXBUS_MultiplexGroup3_FB_CS5; /* FB_CS5 */

config->group4MultiplexControl = kFLEXBUS_MultiplexGroup4_FB_TBST; /* FB_TBST */

config->group5MultiplexControl = kFLEXBUS_MultiplexGroup5_FB_TA; /* FB_TA */

}

The minmum time of FB5 shuld be 0.5 ns.Is it the reasion to make it? How to adujst it?

Thanks and best regards!

zhai