- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- VCCA_UV error on 33907

VCCA_UV error on 33907

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VCCA_UV error on 33907

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

the VCCA_UV error on 33907 was triggered when we are doing test about ESD. details see below:

when we put -6000v voltage ESD on the CAN_H, we found the VCCA_UV error on 33907 was triggered. but when we put -4000v or -8000v voltage ESD on the CAN_H, the VCCA_UV error on 33907 can not be triggered.

and because the VCCA_UV error can not be cleared by READ, we worried that if the VCCA_UV error be triggered on car, we can only cut the power line of our ECU to clear this serious error.

so we want:

1. we want to know the reason why VCCA_UV can be triggered by ESD test, and why only -6000v can trigger the error but -4000v or -8000v can not ?

2. we want to know if the VCCA_UV was triggered , how can we clear it but not need to cut the power line of our ECU.

PS: the 33907 is alway supplied by 12v voltage battery of our ECU on the car.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Liu,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As your saying about that there is a typo in the datasheet saying only cleared by POR, we do not need to unplug the battery connection to clear the VCCA_UV error in our test.

but we still want to know why the VCCA_UV can be triggered by -6000v ESD test?

the newest message is that we can resolve this problem by adding an Common Mode Chip Inductor between CANH and CANL.

We want to know if the UM of 33907 recommend this point ?

PS: The Common Mode Chip Inductor will increase a lot of our bom cost.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Liu,

Could you please share your schematic? This is the minimum before talking about details. In AN4766, we recommend to place an external ESD protection at CANH/L pins. Do you have them? And yes, we recommend to also use the common mode choke for the CAN.

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Tomas,

thanks for your response.

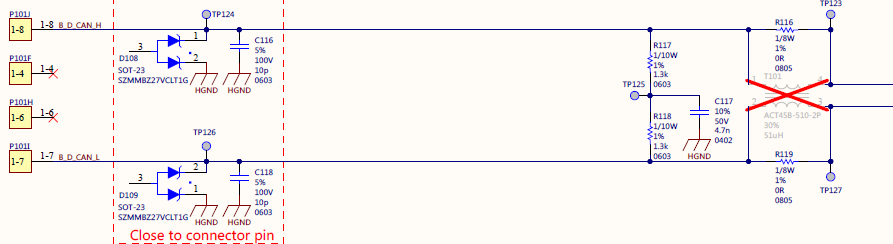

we do not add the common mode choke for the CAN in now our schematic, but we do have the external ESD protection at CANH/L pins. see below:

because we did not found any point at the UM specified the common mode choke need using here , so we did not add the common mode choke in PCB.

so can you help us found the point at the UM specified the common mode choke need to be added?

PS: if we can not found the point at the UM specified the common mode choke need to be added, we think the UM saying that below words is not very accuracy.

because when we do the -6kv ESD test , the VCCA_UV error will make 33907 reset MCU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Liu,

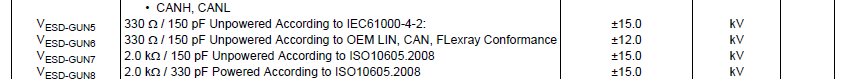

First, the ESD GUN thresholds in the datasheet are verified against specific standards mentioned which request a CLASS D verification, not CLASS A.

- CLASS D means we check after the ESD GUN test we did not degrade the device performance (what is in the datasheet)

- CLASS A means we check during the ESD GUN test the device functionality (what you do)

Second, CAN physical layer requires by default a common mode choke. We would have clearly say in the documentation if this choke would be removed to be choke-less (what is not the case), and not the opposite.

Third, if further discussion is necessary, give us more details like:

- What is your ESD Gun set up (R, C values)?

- What standard do you follow?

- Where do you inject ESD pulse? Connector pin, after cable, air or contact discharge, …

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Tomas,

thank you very much.

the last question is that what is your gist for the words "CAN physical layer requires by default a common mode choke".

after i getting the gist, i think this problem can be closed.

thank you very much again. :smileyhappy: