- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Long wait for PLL to lock with 32kHz crystal on RTC

Long wait for PLL to lock with 32kHz crystal on RTC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm trying to use a 32kHz clock on the RTC pins with an LPC54102. The subject mentionned previously (Wait 15 seconds for PLL to lock the input from 32KHz Crystal ), but I still have this problem, even worst because the wait can be much longer. I need the PLL to generate a 96MHz frequency.

I tried the following :

- Change the SELx as define in remark in the application note (SELP=6, SELI=4 and SELR=0)

=> Still have long wait to lock

- Not using the Chip_Clock_IsSystemPLLLocked() function, and set a 100 ms loop instead.

=> The chip crashes. Need to manually handle the reset pin to be able to re-programming the chip.

I'm currently using the latest LPC open for this chip (v3.03.000).

Thanks for any help.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi eft_flo,

In the periph_pllfract demo, the static void setPllRate(uint32_t rate) function has provided the appropriate flow to setup PLL configuration.

I've already run this demo and it can switch the RTC for the PLL well without spending long time waiting, so please refer to it for details.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

I was wondering if you can share the code you run, then I can replicate the issue on my site.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ping,

To reproduce the problem, use a project example (I use periph_examples, but I don't think this is specific) from the LPCopen. I use the IAR version.

In the file board_sysinit.c add :

void Setup32k (uint32_t iFreq)

{

PLL_CONFIG_T pllConfig;

PLL_SETUP_T pllSetup;

PLL_ERROR_T pllError;

/* IOCON clock left on, this is needed is CLKIN is used. */

Chip_Clock_EnablePeriphClock(SYSCON_CLOCK_IOCON);/* Change clock to IRC to free PLL and configure it */

Chip_Clock_SetMainClockSource(SYSCON_MAINCLKSRC_IRC);

/* Select the PLL input to the EXT clock input */

Chip_Clock_SetSystemPLLSource(SYSCON_PLLCLKSRC_RTC);/* Power down PLL to change the PLL divider ratio */

Chip_SYSCON_PowerDown(SYSCON_PDRUNCFG_PD_SYS_PLL);/* Setup PLL configuration */

pllConfig.desiredRate = iFreq;

/* To the following is taken into account,

configure PLL_CONFIGFLAG_USEINRATE flag to 1 */

pllConfig.InputRate = 32000;

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 21, (IOCON_MODE_PULLUP |

IOCON_FUNC1 |

IOCON_DIGITAL_EN |

IOCON_INPFILT_OFF));

Chip_GPIO_SetPinDIROutput(LPC_GPIO, 0, 21);

/* Change clock source to IRC to be disconnected from PLL */

Chip_Clock_SetCLKOUTSource (SYSCON_CLKOUTSRC_MAINCLK, 1);

pllConfig.flags = PLL_CONFIGFLAG_FORCENOFRACT;

pllError = Chip_Clock_SetupPLLData(&pllConfig, &pllSetup);

if (pllError == PLL_ERROR_SUCCESS) {

pllSetup.flags = PLL_SETUPFLAG_WAITLOCK | PLL_SETUPFLAG_ADGVOLT;

pllError = Chip_Clock_SetupSystemPLLPrec(&pllSetup);

}

/* Change clock to PLL source */

Chip_Clock_SetMainClockSource(SYSCON_MAINCLKSRC_PLLOUT);

}

Change the board_SystemInit that way :

/* Set up and initialize hardware prior to call to main */

void Board_SystemInit(void)

{

/* Setup system clocking and muxing */

Board_SetupMuxing();

Board_SetupClocking();

Setup32k(96000000);

}

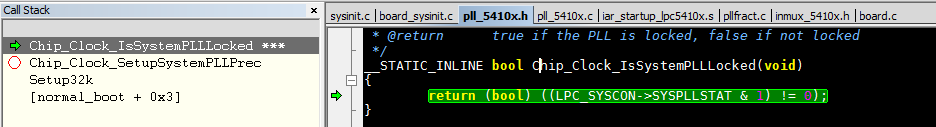

If you set a breakpoint before and after the Setup32k(96000000); function, you will see the software is locked here :

I also tried to add the following to the PLL_ERROR_T Chip_Clock_GetPllConfig function in the file pll_5410x.c:

Right after

/* Setup filtering */

pllFindSel(pllMultiplier, pllBypassFBDIV2, &pllSelP, &pllSelI, &pllSelR);

I add :

/* Specific setting for 32k crystal, from remark from Application Note */

if (finHz == 32768)

{

pllSelP = 6 ;

pllSelI = 1 ;

pllSelR = 0 ;

}

But no improvement from this.

Thanks for help.

Best Regards,

Flo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi eft_flo,

In the periph_pllfract demo, the static void setPllRate(uint32_t rate) function has provided the appropriate flow to setup PLL configuration.

I've already run this demo and it can switch the RTC for the PLL well without spending long time waiting, so please refer to it for details.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ping.

Thanks a lot, it helped me and I manage to make it work.

What was missing me was the following :

-> set after PLL_Power_Down :

/* Turn on the RTC 32K Oscillator to be used as a source for the PLL. */

Chip_SYSCON_PowerUp(SYSCON_PDRUNCFG_PD_32K_OSC);

Chip_Clock_EnableRTCOsc();

and the delay after set the PLL source:

/* Select the 32k_clk as PLL input */

Chip_Clock_SetSystemPLLSource(SYSCON_PLLCLKSRC_RTC);

/* When switching clock sources for the PLL, both the current and new source

must be enabled and requires a small sync time. */

for (int j = 0; j < 0x10000; j++) {}

and to finish the PLL_SETUPFLAG_POWERUP flag for the SetupSystemPLLPrec function.

Thanks again for your help.

Have a nice day, Bye.

Flo.