- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- uboot201603 hangs on Uncompressing Linux... done, booting the kernel

uboot201603 hangs on Uncompressing Linux... done, booting the kernel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

uboot201603 hangs on Uncompressing Linux... done, booting the kernel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

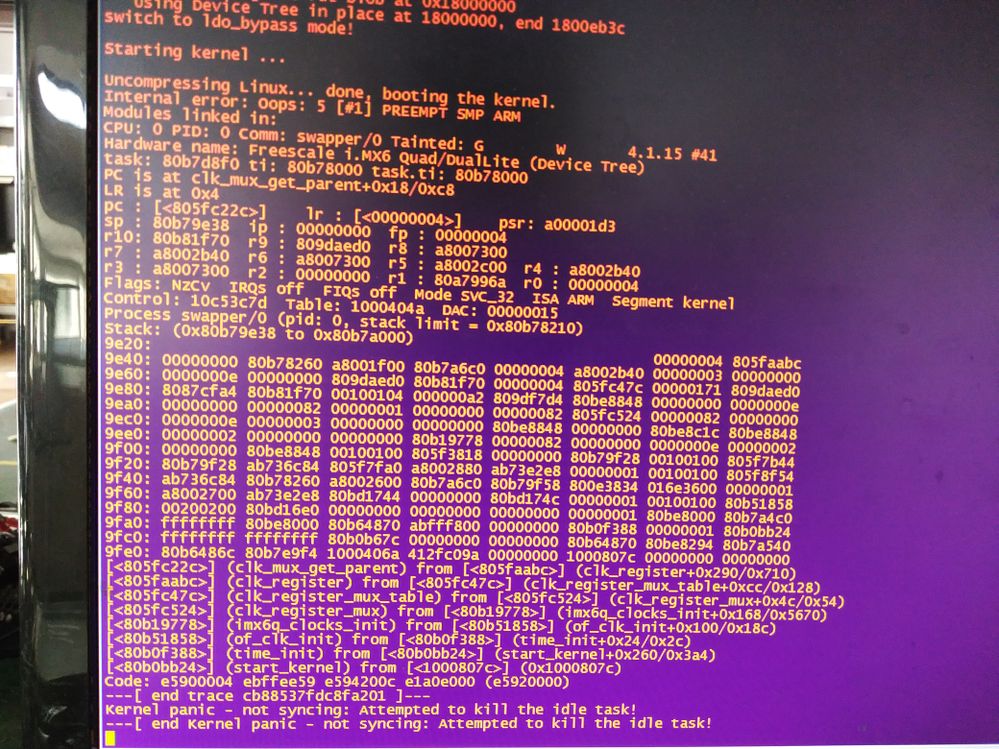

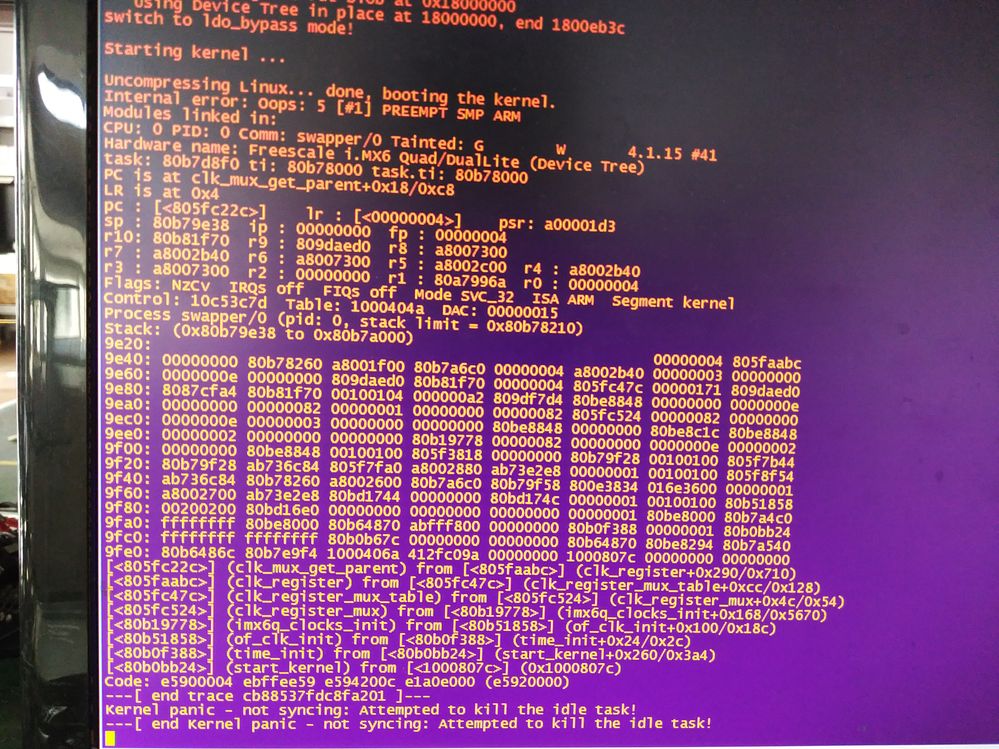

uboot201603 boot zImage(4.1.15) hangs on Uncompressing Linux... done, booting the kernel.it's print error message occasionally,seems it's crashed at clk_mux_get_parent().I‘ll paste log later

zImage boots okay with uboot201404

my board file config

static iomux_v3_cfg_t const uart1_pads[] = {

MX6_PAD_SD3_DAT7__UART1_TX_DATA | MUX_PAD_CTRL(UART_PAD_CTRL),

MX6_PAD_SD3_DAT6__UART1_RX_DATA | MUX_PAD_CTRL(UART_PAD_CTRL),

};

static iomux_v3_cfg_t const usdhc1_pads[] = {

MX6_PAD_SD1_CMD__SD1_CMD | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD1_CLK__SD1_CLK | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD1_DAT0__SD1_DATA0 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD1_DAT1__SD1_DATA1 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD1_DAT2__SD1_DATA2 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD1_DAT3__SD1_DATA3 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

//MX6_PAD_EIM_D16__GPIO3_IO16 | MUX_PAD_CTRL(NO_PAD_CTRL), /* SD1_CD for eq6708 */

MX6_PAD_EIM_D17__GPIO3_IO17 | MUX_PAD_CTRL(NO_PAD_CTRL), /* SD1_CD for epc6708 */

MX6_PAD_EIM_D18__GPIO3_IO18 | MUX_PAD_CTRL(NO_PAD_CTRL), /* WP */

};

static iomux_v3_cfg_t const usdhc3_pads[] = {

MX6_PAD_SD3_CLK__SD3_CLK | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD3_CMD__SD3_CMD | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD3_DAT0__SD3_DATA0 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD3_DAT1__SD3_DATA1 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD3_DAT2__SD3_DATA2 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD3_DAT3__SD3_DATA3 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_GPIO_17__GPIO7_IO12 | MUX_PAD_CTRL(NO_PAD_CTRL), /* CD */

MX6_PAD_GPIO_18__GPIO7_IO13 | MUX_PAD_CTRL(NO_PAD_CTRL), /* WP */

};

static iomux_v3_cfg_t const usdhc4_pads[] = {

MX6_PAD_SD4_CLK__SD4_CLK | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_CMD__SD4_CMD | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_DAT0__SD4_DATA0 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_DAT1__SD4_DATA1 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_DAT2__SD4_DATA2 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_DAT3__SD4_DATA3 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_DAT4__SD4_DATA4 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_DAT5__SD4_DATA5 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_DAT6__SD4_DATA6 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

MX6_PAD_SD4_DAT7__SD4_DATA7 | MUX_PAD_CTRL(USDHC_PAD_CTRL),

};

struct fsl_esdhc_cfg usdhc_cfg[2] = {

// {USDHC1_BASE_ADDR},

{USDHC3_BASE_ADDR},

{USDHC4_BASE_ADDR},

};

/*#define USDHC1_CD_GPIO IMX_GPIO_NR(3, 16) */ /* for eq6708*/

#define USDHC1_CD_GPIO IMX_GPIO_NR(3, 17) /* for epc6708*/

#define USDHC3_CD_GPIO IMX_GPIO_NR(7, 12)

int board_mmc_get_env_dev(int devno)

{

return devno - 2;

}

int mmc_map_to_kernel_blk(int devno)

{

return devno + 2;

}

int board_mmc_getcd(struct mmc *mmc)

{

struct fsl_esdhc_cfg *cfg = (struct fsl_esdhc_cfg *)mmc->priv;

int ret = 0;

switch (cfg->esdhc_base) {

/* case USDHC1_BASE_ADDR:

ret = !gpio_get_value(USDHC1_CD_GPIO);

break;*/

case USDHC3_BASE_ADDR:

ret = !gpio_get_value(USDHC3_CD_GPIO);

break;

case USDHC4_BASE_ADDR:

ret = 1; /* eMMC/uSDHC4 is always present */

break;

}

return ret;

}

int board_mmc_init(bd_t *bis)

{

int ret;

int i;

/*

* According to the board_mmc_init() the following map is done:

* (U-Boot device node) (Physical Port)

* mmc0 SD1

* mmc1 SD3

* mmc2 eMMC

*/

for (i = 0; i < CONFIG_SYS_FSL_USDHC_NUM; i++) {

switch (i) {

/* case 0:

imx_iomux_v3_setup_multiple_pads(

usdhc1_pads, ARRAY_SIZE(usdhc1_pads));

gpio_direction_input(USDHC1_CD_GPIO);

usdhc_cfg[0].sdhc_clk = mxc_get_clock(MXC_ESDHC_CLK);

usdhc_cfg[0].max_bus_width = 4;

break;*/

case 0:

imx_iomux_v3_setup_multiple_pads(

usdhc3_pads, ARRAY_SIZE(usdhc3_pads));

gpio_direction_input(USDHC3_CD_GPIO);

usdhc_cfg[0].sdhc_clk = mxc_get_clock(MXC_ESDHC3_CLK);

usdhc_cfg[0].max_bus_width = 4;

break;

case 1:

imx_iomux_v3_setup_multiple_pads(

usdhc4_pads, ARRAY_SIZE(usdhc4_pads));

usdhc_cfg[1].sdhc_clk = mxc_get_clock(MXC_ESDHC4_CLK);

break;

default:

printf("Warning: you configured more USDHC controllers"

"(%d) then supported by the board (%d)\n",

i + 1, CONFIG_SYS_FSL_USDHC_NUM);

return -EINVAL;

}

ret = fsl_esdhc_initialize(bis, &usdhc_cfg[i]);

if (ret)

return ret;

}

return 0;

}

my environment configs

#define CONFIG_EXTRA_ENV_SETTINGS \

CONFIG_MFG_ENV_SETTINGS \

"fdt_addr=0x18000000\0" \

"fdt_high=0xffffffff\0" \

"bootargs_base=console=" CONFIG_CONSOLE_DEV ",115200 \0" \

"mmcdev="__stringify(CONFIG_SYS_MMC_ENV_DEV)"\0" \

"mmcpart=" __stringify(CONFIG_SYS_MMC_ENV_PART) "\0" \

"mmcroot=" CONFIG_MMCROOT " rootwait rw\0" \

"serverip=" CONFIG_SERVERIP "\0" \

"ipaddr=" CONFIG_IPADDR "\0" \

"ethaddr=00:00:00:00:00:03\0" \

"nfsroot=/home/jiajizhong/nfsdir\0" \

"u-boot=u-boot.imx\0" \

"kernel=zImage\0" \

"loglevel=1\0" \

"splashimage=0x17a00000\0" \

"bmp_file=logo.bmp\0" \

"fec_mode=rgmii\0" \

"adv7611=enable\0" \

"ldb0_panel=dev=ldb,if=RGB24 ldb=sin0\0" \

"ldb1_panel=dev=ldb,if=RGB24 ldb=sin1\0" \

"ldbdul_panel=dev=ldb,if=RGB24 ldb=dul1\0" \

"hdmi_panel=dev=hdmi,1920x1080M@60,if=RGB24\0" \

"lcd_panel=dev=lcd,SEIKO-WVGA,if=RGB24\0" \

"pridis=mxcfb0:dev=ldb,if=RGB24 ldb=sin1\0" \

"secdis=mxcfb1:dev=lcd,SEIKO-WVGA,if=RGB24\0" \

"fdt_file=imx6dl-" CONFIG_BOARD_NAME ".dtb\0" \

"loadimage=fatload mmc ${mmcdev}:${mmcpart} ${loadaddr} ${kernel}\0" \

"loadfdt=fatload mmc ${mmcdev}:${mmcpart} ${fdt_addr} ${fdt_file}\0" \

"bootargs_mmc=setenv bootargs; setenv bootargs ${bootargs_base} root=${mmcroot} "\

"video=${pridis} video=${secdis} loglevel=${loglevel} earlyprintk\0" \

"bootcmd_mmc=run bootargs_mmc; run loadimage; run loadfdt; " \

"bootz ${loadaddr} - ${fdt_addr} \0" \

"bootcmd_tftp=run bootargs_mmc; "\

"tftpboot ${loadaddr} ${kernel}; " \

"tftpboot ${fdt_addr} ${fdt_file}; " \

"bootz ${loadaddr} - ${fdt_addr} \0" \

"bootargs_nfs=setenv bootargs; setenv bootargs ${bootargs_base} " \

"root=/dev/nfs ip=${ipaddr} nfsroot=${serverip}:${nfsroot},v3,tcp\0" \

"bootcmd_nfs=run bootargs_nfs; " \

"tftpboot ${loadaddr} ${kernel}; " \

"tftpboot ${fdt_addr} ${fdt_file}; " \

"bootz ${loadaddr} - ${fdt_addr}\0" \

"bootargs_mem=setenv bootargs; setenv bootargs ${bootargs_base} " \

"rdinit=/etc/inittab enable_wait_mode=off \0" \

"bootcmd_mem=run bootargs_mem; " \

"tftpboot ${loadaddr} uImage.ramdisk; " \

"tftpboot ${fdt_addr} rootfs.ramdisk; " \

"bootm ${loadaddr} ${fdt_addr}\0" \

"update_uboot=tftpboot ${loadaddr} ${u-boot};" \

"sf probe; sf erase 0 0x200000;" \

"sf write ${loadaddr} 0x400 0x80000\0" \

"bootcmd=run bootcmd_mmc \0"

#endif

Original Attachment has been moved to: mx6eq6708_common.h.zip

Original Attachment has been moved to: mx6eq6708.h.zip

Original Attachment has been moved to: mx6eq6708.c.zip

Original Attachment has been moved to: mx6eq6708android_common.h.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

had you tried ddr test for board

https://community.freescale.com/docs/DOC-105652

and rebuilt uboot with new calibration coefficients in

uboot../board_name/*.cfg file.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------