- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Unable to wake K20 from LLS power mode without debugger

Unable to wake K20 from LLS power mode without debugger

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to put the K20 in low-leakage stop mode and then wake it with the LLWU. This code works fine when I am using the debugger but without the debugger I get stuck somewhere between LED1_ON and LED0_ON. Any ideas?

#include <common.h>

// Include the cpu / board header file

#include <cpu/MK20D10.h>

#include <board/escort_zr5.h>

#include <string.h>

#include "i2c.h"

void enter_lls(void);

void deepsleep(void);

void sleep(void);

int main(void)

{

volatile unsigned int dummyread;

i2c_init(0, ACCEL_SLAVE_ADDRESS, 400000);

I2CAccelInit();

DBG_LED1_ON;

// Enable PC3 as falling edge wakeup to LLWU

LLWU_PE2 |= LLWU_PE2_WUPE7(2);

// Disable the clock monitor

MCG_C6 &= ~MCG_C6_CME0_MASK;

// Put the processor in low-leakage stop mode

enter_lls();

//

// Waiting for a motion interrupt from the accelerometer

//

DBG_LED0_ON; // Tell the world we're awake

while(1);

return 0;

}

/***************************************************************/

/*

* Configures the ARM system control register for WAIT(sleep)mode

* and then executes the WFI instruction to enter the mode.

*

* Parameters:

* none

*

*/

void sleep (void)

{

/* Clear the SLEEPDEEP bit to make sure we go into WAIT (sleep)

* mode instead of deep sleep.

*/

SCB_SCR &= ~SCB_SCR_SLEEPDEEP_MASK;

#ifdef CMSIS

__wfi();

#else

/* WFI instruction will start entry into WAIT mode */

asm("WFI");

#endif

}

/***************************************************************/

/*

* Configures the ARM system control register for STOP

* (deepsleep) mode and then executes the WFI instruction

* to enter the mode.

*

* Parameters:

* none

*

*/

void deepsleep (void)

{

/* Set the SLEEPDEEP bit to enable deep sleep mode (STOP) */

SCB_SCR |= SCB_SCR_SLEEPDEEP_MASK;

#ifdef CMSIS

__wfi();

#else

/* WFI instruction will start entry into STOP mode */

asm("WFI");

#endif

}

/***************************************************************/

/* LLS mode entry routine. Puts the processor into LLS mode from

* normal Run mode or VLPR.

*

* Mode transitions:

* RUN to LLS

* VLPR to LLS

*

* Wake-up from LLS mode is controlled by the LLWU module. Most

* modules cannot issue a wake-up interrupt in LLS mode, so make

* sure to set up the desired wake-up sources in the LLWU before

* calling this function.

*

* Parameters:

* none

*/

void enter_lls(void)

{

volatile unsigned int dummyread;

/* Write to PMPROT to allow LLS power modes this write-once

bit allows the MCU to enter the LLS low power mode*/

SMC_PMPROT = SMC_PMPROT_ALLS_MASK;

/* Set the (for MC1) LPLLSM or

(for MC2)STOPM field to 0b011 for LLS mode

Retains LPWUI and RUNM values */

SMC_PMCTRL &= ~SMC_PMCTRL_STOPM_MASK ;

SMC_PMCTRL |= SMC_PMCTRL_STOPM(0x3) ;

/*wait for write to complete to SMC before stopping core */

dummyread = SMC_PMCTRL;

/* Now execute the stop instruction to go into LLS */

deepsleep();

}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ryanlush,

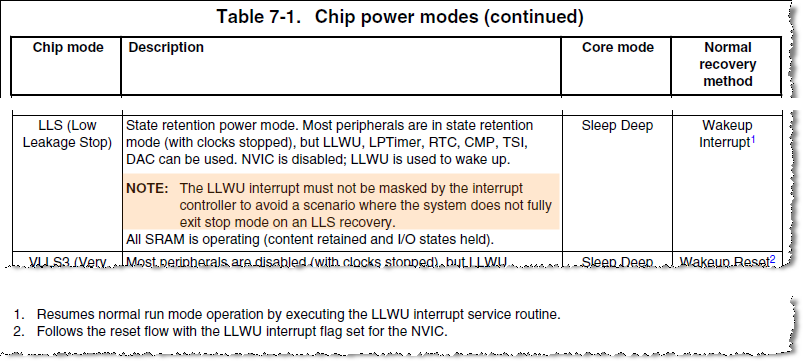

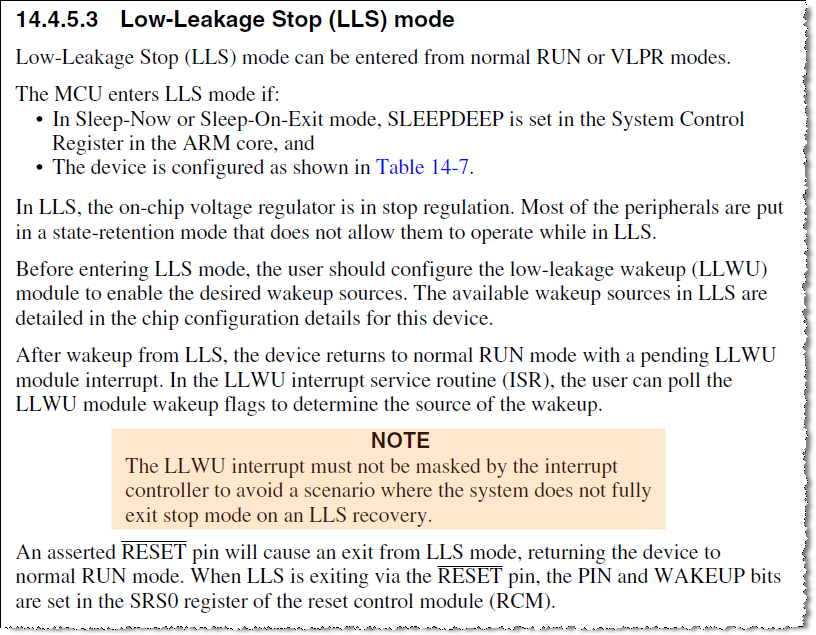

From the reference manual: "NOTE The LLWU interrupt must not be masked by the interrupt controller to avoid a scenario where the system does not fully exit stop mode on an LLS recovery."

The LLWU ISR is required when waking from LLS or VLLSx low-power modes.

We're glad to hear you have the wake-up working now. Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Maybe I'm missing something but the datasheet doesn't explicitly say that you need to use the LLWU interrupt to wake the processor. When using the debugger it wakes up but without the debugger it seems you need to enable and handle the interrupt. That was all I did to get things working.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

“The LLWU interrupt must not be masked by the interrupt controller to avoid a scenario where the system does not fully exit stop mode on an LLS recovery.”

Best Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I read that several times when I was trying to figure this out. As you've all so clearly pointed out, it's mentioned over and over in the datasheet. It's still about as clear as mud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ryanlush,

From the reference manual: "NOTE The LLWU interrupt must not be masked by the interrupt controller to avoid a scenario where the system does not fully exit stop mode on an LLS recovery."

The LLWU ISR is required when waking from LLS or VLLSx low-power modes.

We're glad to hear you have the wake-up working now. Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ryan,

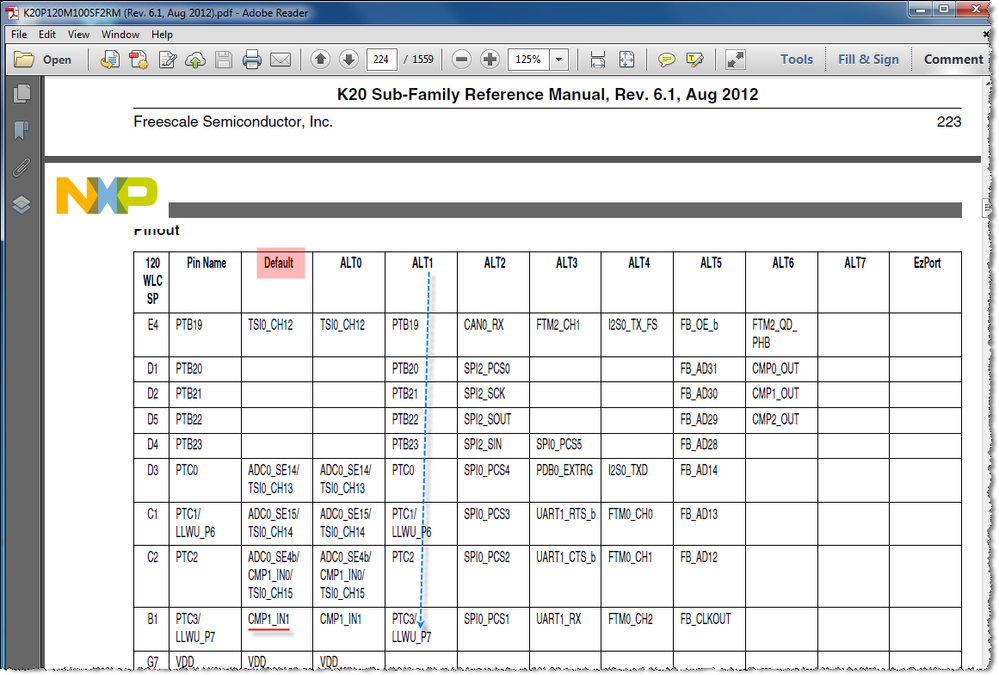

The PTC3/LLWU_P7 pin is default as CMP1_IN1 function.

Have you try to configure PORTx_PCRn[MUX] before using LLWU?

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes. And like I said, it wakes up with this pin when on the debugger.

![PORTx_PCRn[MUX].png PORTx_PCRn[MUX].png](/t5/image/serverpage/image-id/12821iD221C8F322D75535/image-size/large?v=v2&px=999)