- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- Unable to recover NOR Flash on T4240RDB Rev 2.0 With CW-10.5.1 and RCW (Jtag Chain) Override method

Unable to recover NOR Flash on T4240RDB Rev 2.0 With CW-10.5.1 and RCW (Jtag Chain) Override method

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Unable to recover NOR Flash on T4240RDB Rev 2.0 With CW-10.5.1 and RCW (Jtag Chain) Override method

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

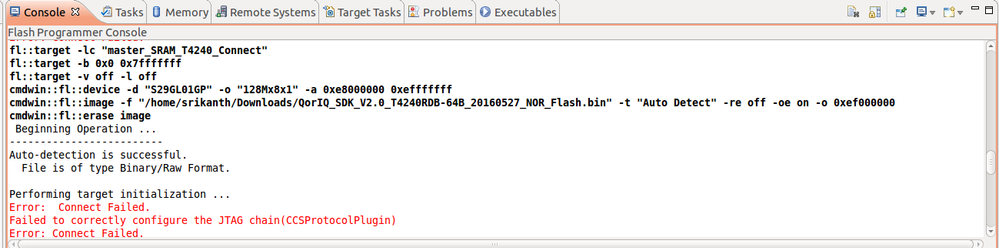

Unable to recover NOR flash for T4240rdb with CodeWarrior 10.5.1 with Host System Ubuntu 14.04.5.

Using Codewarrior USB TAP and the flash programmer to flash a NOR flash image to my t4240rdb board

Getting following error "Failed to correctly configure the JTAG chain(CCSProtocalPlugin)"

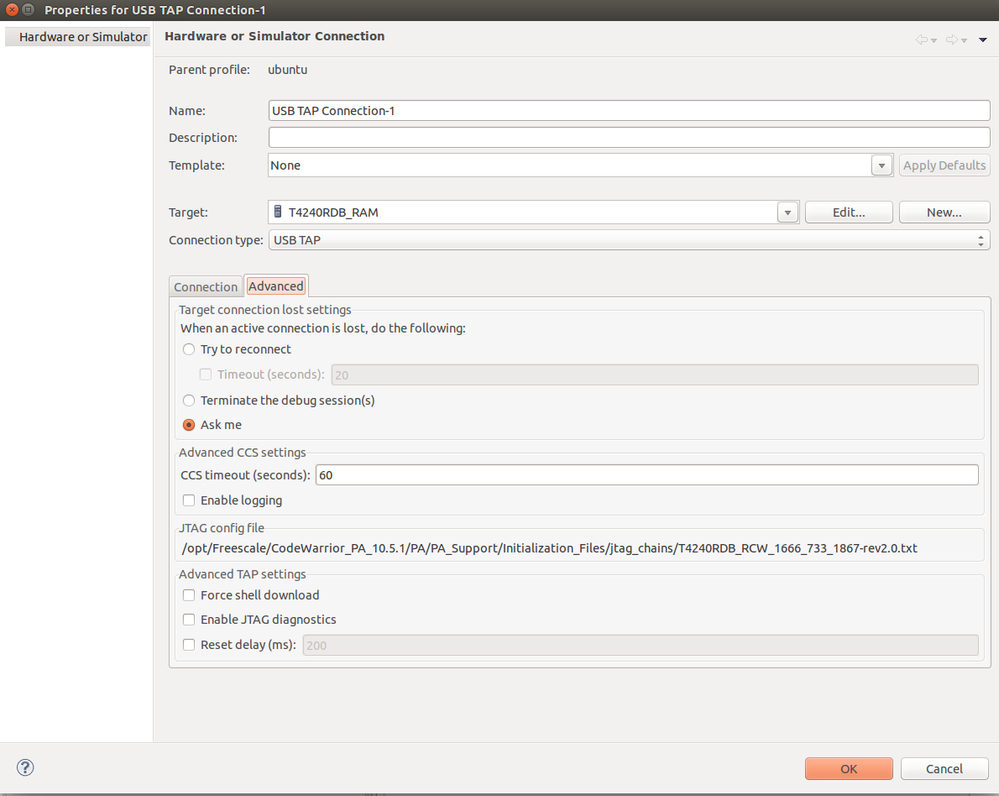

Created BareBoard Project and used T4240RDB_init_sram.tcl as initialization file and chosen CodeWarrior USB TAP to be the connection type(Both when creating the project or change the settings after creating are OK).

For overriding RCW used T4240RDB_RCW...-rev2.0.txt in the JTAG file configuration panel.

Attached is ccs logs

Request for help in recovering board by properly flashing NOR flash with help of Code Warrior.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Request for help on proceeding further.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The RCW override is not working, unless the latest CPLD image is used. To get the latest CPLD image you should contact your NXP representative.

If you want to recover the RCW in EEPROM, you can fallow the steps below:

- In a linux environmental write the sdcard uboot to a SD card

- Insert SD card into T4RDB board and set SW3[4]=0 and SW2[1]=1 to boot uboot

- In Uboot, load the RCW image to ram then write it to EEPROM using i2c write <load_addr> 50 .01 78

- Set SW3[4]=0 and reset

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Adrian,

Presently we don't have sd_card slot working.

If we cant recover with RCW override then do we have any other way of recovering the board.

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please contact your NXP representative and a new CPLD image can be provided. The latest CPLD image allow RCW source from NOR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Adrian,

I have received latest pof file from NXP representative which will support RCW override.

Request the procedure for flashing this pof file.

Can we use code-warrior with USB tap connection or do we need to use Usb-blaster?

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Updating the pof file is not possible using CodeWarrior/USB tap. Internally, we used some programmer from Altera (Quartus).

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Adrian,

Updated pof file with Altera (Quartus) Programmer which was successful.

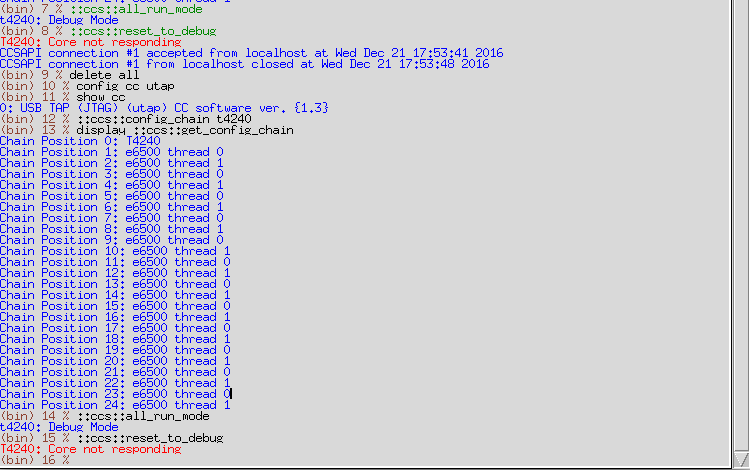

But RCW override is failing.Following is ccs log

verbose logging

| ccs log |

|---|

| CCSAPI connection #1 accepted from localhost at Mon Jan 16 20:46:24 2017 check_min_version(serverh=0,*version) api version: 00000004 00000006 get_connection_count(serverh=0,cc_index=0,*count) count:1 available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} available_connections(serverh=0,*count,*cc) connections: get_connection_count(serverh=0,cc_index=0,*count) count:1 available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} available_connections(serverh=0,*count,*cc) connections: available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} delete_cc(serverh=0,cc=0) setup_cc(serverh=0,config_string= utap:0 ) available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} cc_version(serverh=0,cc_index=0,index=-240214688,*version) available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} available_connections(serverh=0,*count,*cc) connections: {0,70,0x00000000} config_server(config_reg=0,config_data=0x000027F6) get_config_chain(serverh=0,cc=0) config_chain(serverh=0,cc=0,count=1,*devlist,*generic) devlist: t4amp config_template(coreh.{serverh=0,cc_index=0,chain_pos=0},config_reg=2,config_data=0x00000001) write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210001,size=4,*reg) reg: 16070019 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210002,size=4,*reg) reg: 18101916 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210003,size=4,*reg) reg: 00000000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210004,size=4,*reg) reg: 00000000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210005,size=4,*reg) reg: 70701050 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210006,size=4,*reg) reg: 00448C00 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210007,size=4,*reg) reg: 0C020000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210008,size=4,*reg) reg: F5000000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210009,size=4,*reg) reg: 00000000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210010,size=4,*reg) reg: EE0000EE write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210011,size=4,*reg) reg: 00000000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210012,size=4,*reg) reg: 000287FC write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210013,size=4,*reg) reg: 00000000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210014,size=4,*reg) reg: 50000000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210015,size=4,*reg) reg: 00000000 write_register(coreh.{serverh=0,cc_index=0,chain_pos=0},index=210016,size=4,*reg) reg: 00000028 reset_to_debug(serverh=0,cc=0) ERROR(39): Subcore error encountered during multicore operation parse_error_ext(coreh.{serverh=0,cc_index=0,chain_pos=0}, 39) error: T4240: Scan timeout get_subcore_error(serverh=0,cc=0,*error,*chain_pos) error: Scan timeout chain_pos: 0 reset_to_debug(serverh=0,cc=0) ERROR(39): Subcore error encountered during multicore operation parse_error_ext(coreh.{serverh=0,cc_index=0,chain_pos=0}, 39) error: T4240: Scan timeout get_subcore_error(serverh=0,cc=0,*error,*chain_pos) error: Scan timeout chain_pos: 0 reset_to_debug(serverh=0,cc=0) ERROR(39): Subcore error encountered during multicore operation parse_error_ext(coreh.{serverh=0,cc_index=0,chain_pos=0}, 39) error: T4240: Scan timeout get_subcore_error(serverh=0,cc=0,*error,*chain_pos) error: Scan timeout chain_pos: 0 CCSAPI connection #1 from localhost closed at Mon Jan 16 20:46:40 2017 |

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please confirm your cpld image is T4240RDB_V7p0.pof (T4240RDB_2016_0602_0933).

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Adrian,

The cpld Image which I received and flashed is T4240RDB_V7p0.pof(Release notes mentions T4240RDB_2016_0602_0933).

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Take the script attached and run it in ccs using:

(bin) 56 % source C:/CCS_RCW_override_t4240rdb.tcl

My test board is set for NOR boot:

SW2: ON ON OFF OFF

SW3: OFF OFF OFF ON

SW4: ON ON ON ON

SW1: ON ON ON ON

ccs should report no error when running the script. I tested on my side and RCW override is working fine with the new cpld image.

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Adrian,

You mean switch setting like below.In previous reply you have started from SW2 to SW5

SW1: ON ON OFF OFF

SW2: OFF OFF OFF ON

SW3: ON ON ON ON

SW4: ON ON ON ON.

After setting above switch setting running the script shared resulted in following

| Script log |

|---|

| 0: USB TAP (JTAG) (utap) CC software ver. {1.3} Chain Position 0: T4AMP SoC Chain Position 1: e6500 thread 0 Chain Position 2: e6500 thread 1 Chain Position 3: e6500 thread 0 Chain Position 4: e6500 thread 1 Chain Position 5: e6500 thread 0 Chain Position 6: e6500 thread 1 Chain Position 7: e6500 thread 0 Chain Position 8: e6500 thread 1 Chain Position 9: e6500 thread 0 Chain Position 10: e6500 thread 1 Chain Position 11: e6500 thread 0 Chain Position 12: e6500 thread 1 Chain Position 13: e6500 thread 0 Chain Position 14: e6500 thread 1 Chain Position 15: e6500 thread 0 Chain Position 16: e6500 thread 1 Chain Position 17: e6500 thread 0 Chain Position 18: e6500 thread 1 Chain Position 19: e6500 thread 0 Chain Position 20: e6500 thread 1 Chain Position 21: e6500 thread 0 Chain Position 22: e6500 thread 1 Chain Position 23: e6500 thread 0 Chain Position 24: e6500 thread 1 T4AMP SoC: Scan timeout |

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Just correct my previous post. The SW settings I'm using:

SW2: ON ON OFF OFF

SW3: OFF OFF OFF ON

SW4: ON ON ON ON

SW1: ON ON ON ON

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Adrian,

Getting "T4AMP SoC: Scan timeout" with Switch settings specified.

SW2: ON ON OFF OFF

SW3: OFF OFF OFF ON

SW4: ON ON ON ON

SW1: ON ON ON ON

| Header 1 |

|---|

bin) 6 % source /home/tester/CCS_RCW_override_t4240rdb.tcl T4AMP SoC: Scan timeout |

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the previous SW settings I miss the SYSCLK setting. So please use the following:

SW2: ON ON OFF OFF

SW3: OFF OFF OFF ON

SW4: ON ON ON ON

SW1: ON ON OFF OFF

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

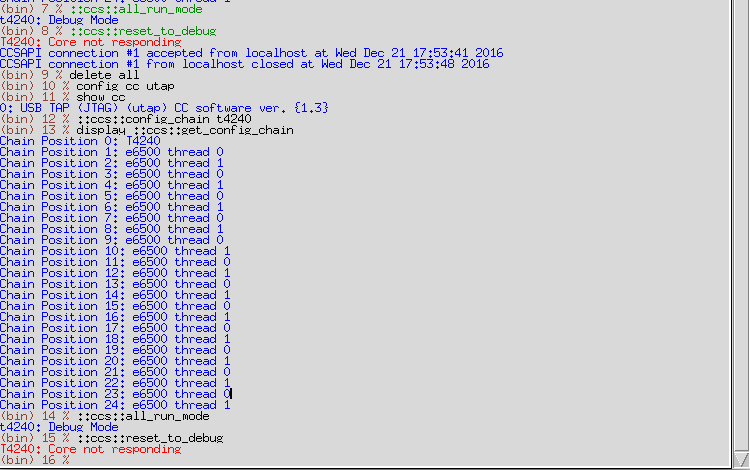

Still facing "Scan Timeout" ,even after modifying switch settings specified as

SW2: ON ON OFF OFF

SW3: OFF OFF OFF ON

SW4: ON ON ON ON

SW1: ON ON OFF OFF

Following is the log

(bin) 20 % source /home/Downloads/CCS_RCW_override_t4240rdb.tcl

0: USB TAP (JTAG) (utap) CC software ver. {1.3}

Chain Position 0: T4AMP SoC

Chain Position 1: e6500 thread 0

Chain Position 2: e6500 thread 1

Chain Position 3: e6500 thread 0

Chain Position 4: e6500 thread 1

Chain Position 5: e6500 thread 0

Chain Position 6: e6500 thread 1

Chain Position 7: e6500 thread 0

Chain Position 8: e6500 thread 1

Chain Position 9: e6500 thread 0

Chain Position 10: e6500 thread 1

Chain Position 11: e6500 thread 0

Chain Position 12: e6500 thread 1

Chain Position 13: e6500 thread 0

Chain Position 14: e6500 thread 1

Chain Position 15: e6500 thread 0

Chain Position 16: e6500 thread 1

T4AMP SoC: Scan timeout

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You could try different selection for SYSCLK and DDRCLK, maybe the core will respond.

0000 66.67 66.67

0001 66.67 100

0010 66.67 125

0011 (Default) 66.67 133.33

0100 100 66.67

0101 100 100

0110 100 125

0111 100 133.33

1000 125 66.67

1001 125 100

1010 125 125

1011 125 133.33

1100 133.33 66.67

1101 133.33 100

1110 133.33 125

1111 133.33 133.33

If this is not working, my guess is the board have some hardware issues.

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For all the above switch setting got "T4AMP SoC: Scan timeout" on running CCS_RCW_override_t4240rdb.tcl in ccs.

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

On my side it works ok using the below two cases:

1. Board set to hardcoded rcw, with not using the write_reg in the tcl script

SW1: OFF OFF ON ON

SW2: ON OFF OFF OFF

SW3: OFF OFF OFF OFF

SW4: OFF OFF OFF OFF

2. Board set to boot for NOR, with write_reg in the tcl script

SW1: OFF OFF ON ON

SW2: ON ON OFF OFF

SW3: OFF OFF OFF OFF

SW4: OFF OFF OFF OFF

For both above cases, ccs is not returning "Scan timeout"

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Adrian,

Switch setting are as specified in T4240RDB_aeabi_README.txt (\PA\PA_Support\Readme\QorIQ_T4\).

| switch setting |

|---|

| NOR_BOOT: --------- SW1 : 0x3 = 1100 SW2 : 0xF = 1111 SW3 : 0xF = 1111 SW4 : 0xF = 1111 Note: ON side is 0, the other side is 1. |

Thanks,

Hemanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Depending on CPLD image RCW override is not supportted. Try using hardcoded from dip switches. For that set SW2[1:2] = 01 and SW3[4] = 1, where 0 is ON and 1 is OFF.

Adrian