- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Kinetis Controller Not Replying Properly in SPI Slave Mode

Kinetis Controller Not Replying Properly in SPI Slave Mode

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SOLVED

12-15-2016

11:44 PM

576 Views

waqasbutt

Contributor II

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

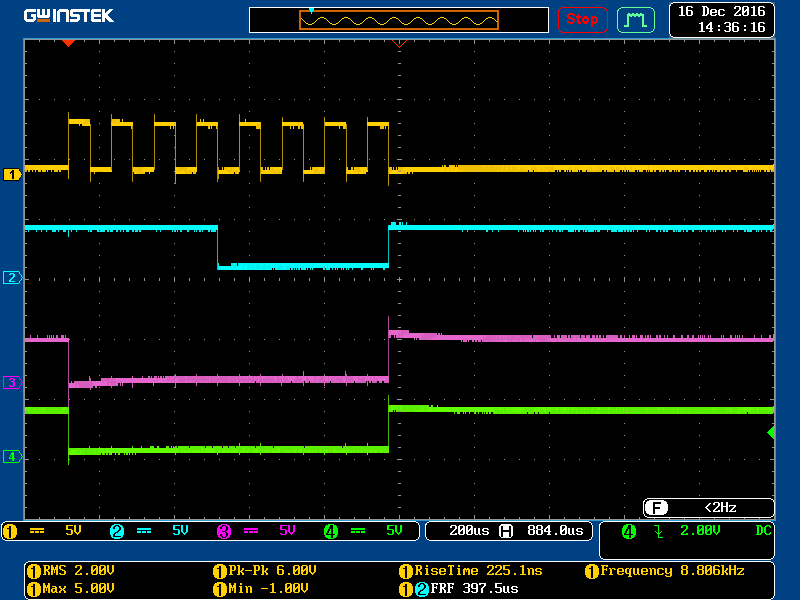

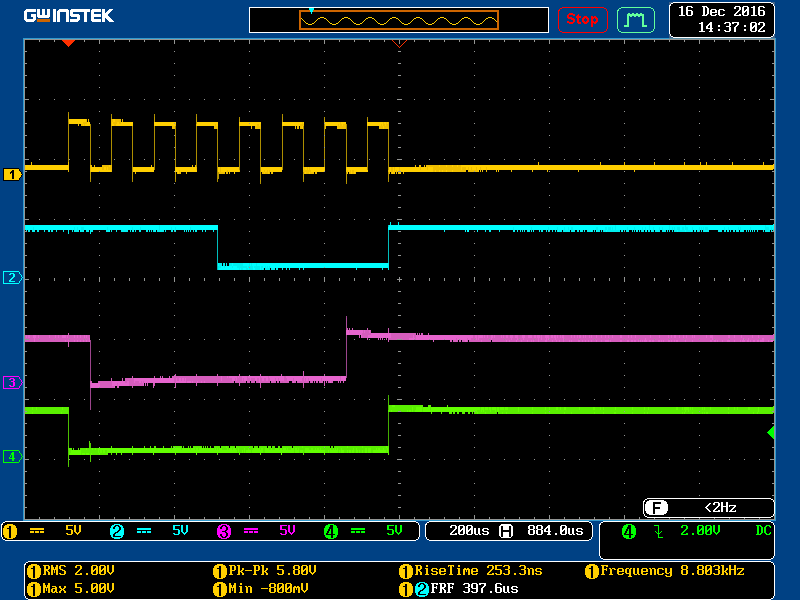

I am using K20 series controller. In slave mode the controller keeps sending the first value that has been pushed through PUSHR_SLAVE. It never updates.

The slave is receiving data correctly which can be seen through the oscilloscope. The settings CPHA and CPOL also match in slave and master

Images of Oscilloscope

1. Yellow (Clk)

2. Blue (Slave Out)

3. Purple (Master Out)

4. Green (Chip Select)

Slave Code is as follows

SLAVE:

// Initialization

void SPI1_Init(void)

{

/* SIM_SCGC6: DSPI1=1 */

SIM_SCGC6 |= SIM_SCGC6_DSPI1_MASK;

/* SPI1_MCR: MSTR=0,CONT_SCKE=0,DCONF=0,FRZ=0,MTFE=0,PCSSE=0,ROOE=0,??=0,??=0,PCSIS=0,DOZE=0,MDIS=0,DIS_TXF=0,DIS_RXF=0,CLR_TXF=0,CLR_RXF=0,SMPL_PT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HALT=1 */

SPI1_MCR = SPI_MCR_DCONF(0x00) |

SPI_MCR_PCSIS(0x00) |

SPI_MCR_SMPL_PT(0x00) |

SPI_MCR_HALT_MASK;

/* SPI1_MCR: MSTR=0,CONT_SCKE=0,DCONF=0,FRZ=0,MTFE=0,PCSSE=0,ROOE=0,??=0,??=0,PCSIS=0x0F,DOZE=0,MDIS=0,DIS_TXF=1,DIS_RXF=1,CLR_TXF=1,CLR_RXF=1,SMPL_PT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HALT=1 */

SPI1_MCR = SPI_MCR_DCONF(0x00) |

SPI_MCR_PCSIS(0x0F) |

SPI_MCR_DIS_TXF_MASK |

SPI_MCR_DIS_RXF_MASK |

SPI_MCR_CLR_TXF_MASK |

SPI_MCR_CLR_RXF_MASK |

SPI_MCR_SMPL_PT(0x00) |

SPI_MCR_HALT_MASK;

/* SPI1_TCR: SPI_TCNT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SPI1_TCR = SPI_TCR_SPI_TCNT(0x00);

/* SPI1_CTAR1: DBR=0,FMSZ=0x0F,CPOL=0,CPHA=0,LSBFE=0,PCSSCK=0,PASC=0,PDT=0,PBR=0,CSSCK=0,ASC=0,DT=0,BR=0 */

SPI1_CTAR1 = SPI_CTAR_FMSZ(0x0F) |

SPI_CTAR_PCSSCK(0x00) |

SPI_CTAR_PASC(0x00) |

SPI_CTAR_PDT(0x00) |

SPI_CTAR_PBR(0x00) |

SPI_CTAR_CSSCK(0x00) |

SPI_CTAR_ASC(0x00) |

SPI_CTAR_DT(0x00) |

SPI_CTAR_BR(0x00);

/* SPI1_CTAR0_SLAVE: FMSZ=7,CPOL=0,CPHA=0 */

SPI1_CTAR0_SLAVE = (uint32_t)((SPI1_CTAR0_SLAVE & (uint32_t)~(uint32_t)(

SPI_CTAR_SLAVE_FMSZ(0x18) |

SPI_CTAR_SLAVE_CPOL_MASK |

SPI_CTAR_SLAVE_CPHA_MASK

)) | (uint32_t)(

SPI_CTAR_SLAVE_FMSZ(0x07)

));

/* SPI1_SR: TCF=1,TXRXS=1,??=0,EOQF=1,TFUF=1,??=0,TFFF=1,??=0,??=0,??=0,??=0,??=0,RFOF=1,??=0,RFDF=1,??=0,TXCTR=0,TXNXTPTR=0,RXCTR=0,POPNXTPTR=0 */

SPI1_SR = SPI_SR_TCF_MASK |

SPI_SR_TXRXS_MASK |

SPI_SR_EOQF_MASK |

SPI_SR_TFUF_MASK |

SPI_SR_TFFF_MASK |

SPI_SR_RFOF_MASK |

SPI_SR_RFDF_MASK |

SPI_SR_TXCTR(0x00) |

SPI_SR_TXNXTPTR(0x00) |

SPI_SR_RXCTR(0x00) |

SPI_SR_POPNXTPTR(0x00);

/* SPI1_RSER: TCF_RE=0,??=0,??=0,EOQF_RE=0,TFUF_RE=0,??=0,TFFF_RE=0,TFFF_DIRS=0,??=0,??=0,??=0,??=0,RFOF_RE=0,??=0,RFDF_RE=1,RFDF_DIRS=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SPI1_RSER = SPI_RSER_RFDF_RE_MASK;

/* SPI1_MCR: HALT=0 */

SPI1_MCR &= (uint32_t)~(uint32_t)(SPI_MCR_HALT_MASK);

}

// Service Routine

PE_ISR(INT_SPI1_HANDLER)

{

uint32_t receivedValue = SPI1_POPR;

uint8_t valueToSend = 0;

SPI1_SR = SPI_SR_RFDF_MASK | SPI_SR_TCF_MASK;

if(receivedValue == 0x81)

valueToSend = 0xF0;

else

valueToSend = 0x0F;

while((SPI1_SR & SPI_SR_TFFF_MASK)==0);

SPI1_PUSHR_SLAVE = valueToSend;

}

Solved! Go to Solution.

1 Solution

12-16-2016

04:42 AM

387 Views

waqasbutt

Contributor II

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Problem solved.

It was a hardware problem. cs pin was not correctly attached

1 Reply

12-16-2016

04:42 AM

388 Views

waqasbutt

Contributor II

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Problem solved.

It was a hardware problem. cs pin was not correctly attached