- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Can we configure Fault interrupt as rising edge

Can we configure Fault interrupt as rising edge

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can we configure Fault interrupt as rising edge

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Support team,

I am working on S32k freedom board(FRDMPK144-100).I have implemented fault for PWM channels.It is generating fault interrupt as long as fault signal is enable if i don't disable the fault interrupt in ISR then core is busy in servicing back to back interrupt from fault module.if i disable the fault interrupt and enable it back in application then i couldn't be able to receiving ICU interrupt which i need to capture always as i have some input frequency on ICU. I wanted to receive interrupt only once when fault signal goes low to high.

Please guide.

BR,

Nitin verma

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

the fault input signal is edge sensitive, not level sensitive. I think that the section "39.5.18 Fault control" in reference manual is clear enough. Have you cleared the flags as mentioned in RM?

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Lukas,

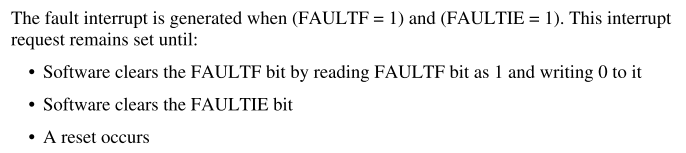

I cleared the FAULTF bit by reading FAULTF bit in FMS register and then writing 0 to it using FTM_HAL_ClearFaultsIsr(ftmBase) given API.I saw in FMS register in watch window still FAULTF bit and FAULTF1(in my case) are high.As per RM The fault interrupt is generated when (FAULTF = 1) and (FAULTIE = 1) hence the fault interrupt generated till fault signal persists and behaving like level trigger interrupt until i disable Fault interrupt.Please correct me if i am wrong.

BR,

Nitin verma.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

are you sure there are no glitches on the signal? Have you tried to configure filter (FLTPS in FTM_SC) to filter glitches? Have you tried to disconnect the signal and connect some testing signal from generator?

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Lukas,

There is no glitch in the fault signal.I am a generating a low frequency signal (10 Hz) by toggling GPIO of freedom board and giving this signal as a fault input to the fault module.I have checked on MSO there is no glitch at all in signal.I think there is not required such a smooth square wave given from freedom board.I don't have function generator with me so can't give external input.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

sorry for delay caused by vacations during Christmas time.

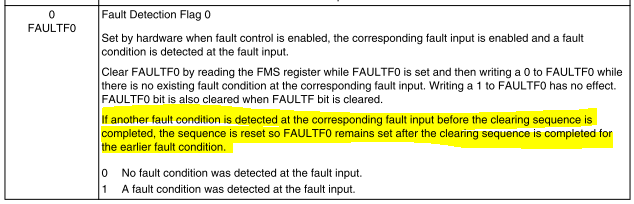

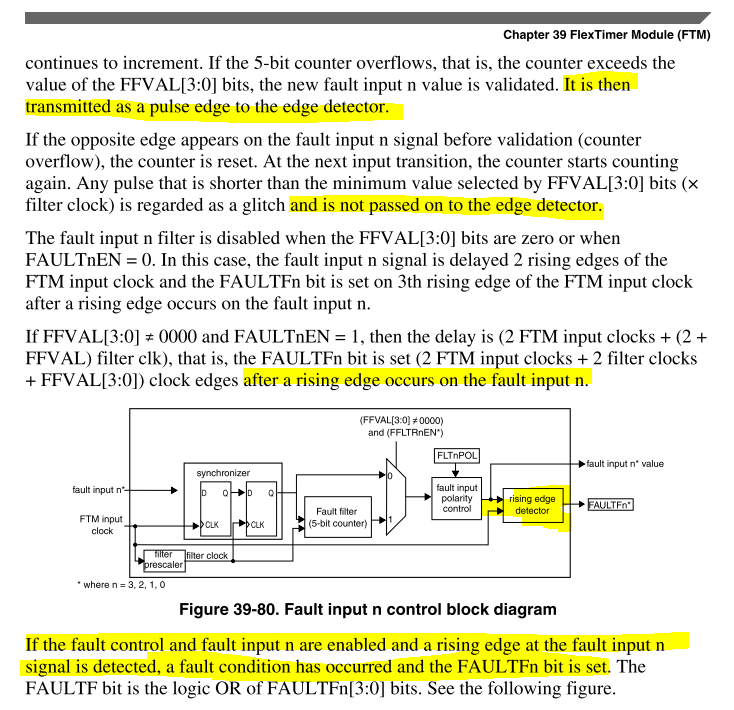

I have done deeper research and the result is that the behavior is correct. The fault interrupt itself is really edge sensitive. Then, if the fault condition is still present, the flag cannot be cleared:

So, if the fault pin is still asserted, the interrupt handler will be executed again and again until the fault pin is deasserted. It makes sense because the fault is still present. Now it is application problem - the fault must be either solved somehow in the interrupt handler, so the flag can be cleared or you can disable the interrupt and then use polling method to solve the problem.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Lukas,

Wish you a very happy and prosperous new year.

It's clear now how Fault interrupt is generating if fault signal is asserted.I didn't find anywhere in RM if Fault interrupt is edge sensitive.

I would appreciate if you can share the page where it has been mentioned.

BR,

Nitin verma

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nitin,

happy new year to you too :-)

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot for your prompt and significant reply.